ORDER NO. **ARP1758**

# LASERVISION PLAYER

- This manual is applicable to the KUC type.

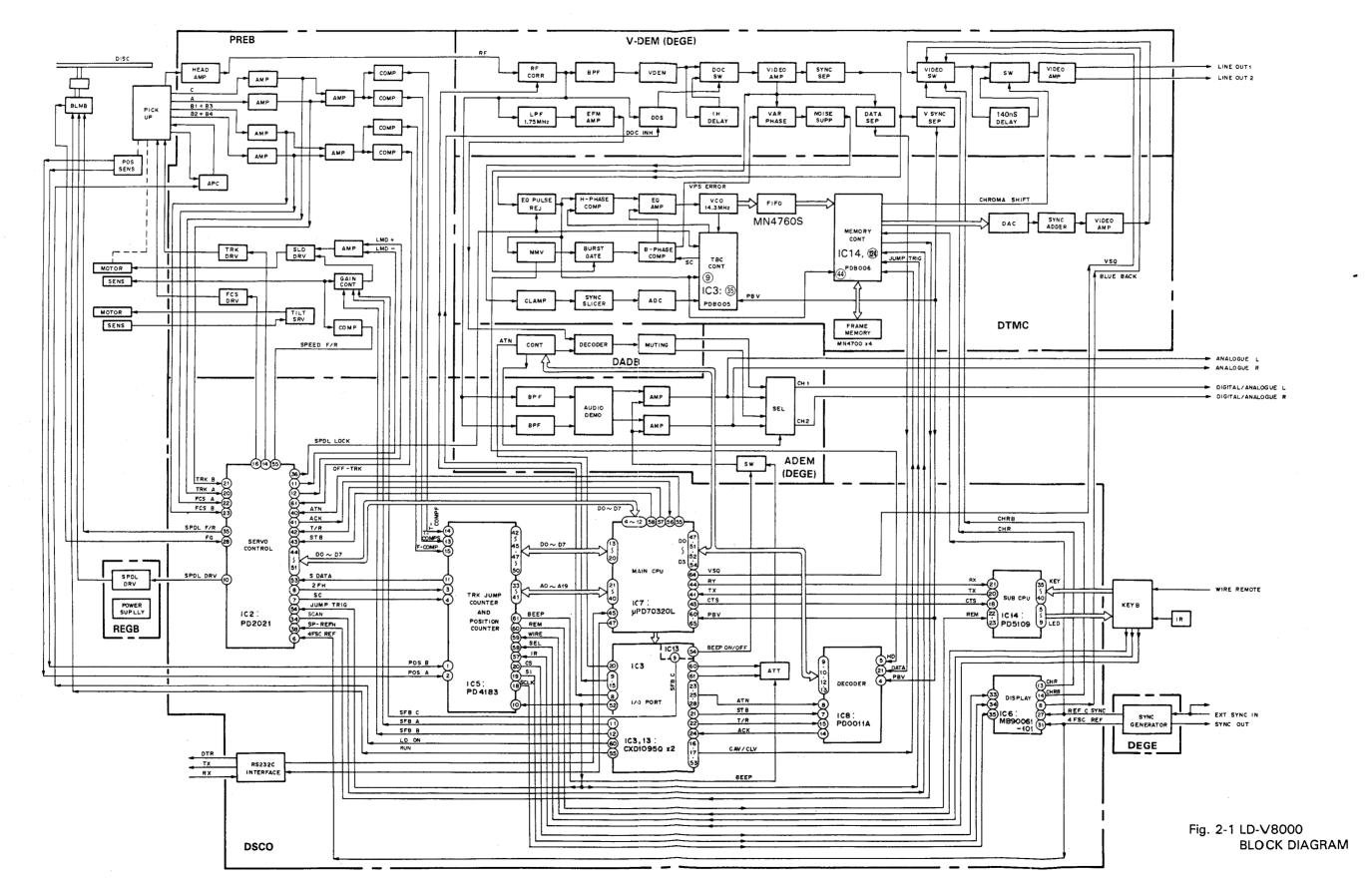

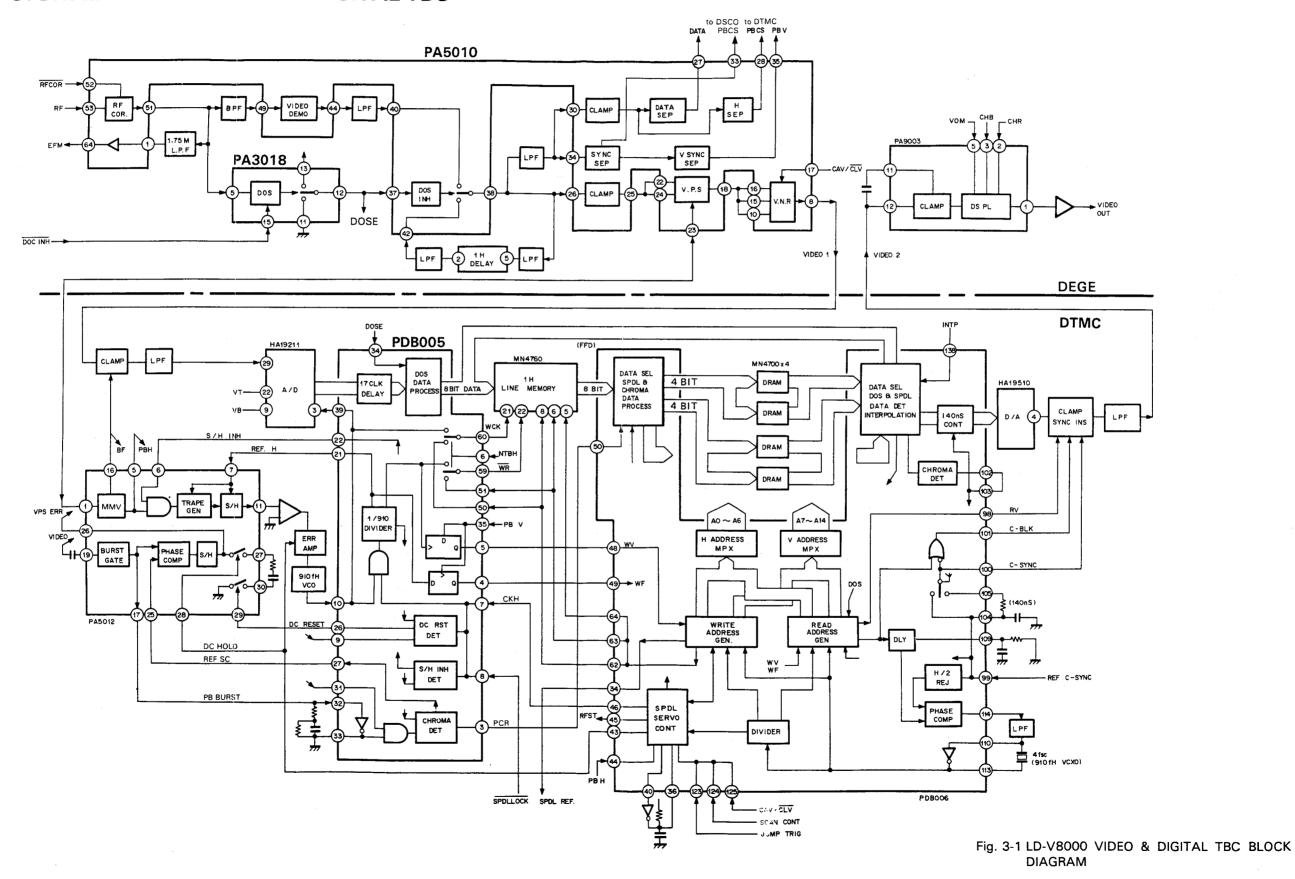

- For the circuit and mechanism descriptions, refer to the LD-V8000 service guide (ARP1759).

#### **CONTENTS**

| 1. SAFETY INFORMATION 2 2. EXPLODED VIEWS AND PARTS LIST 3 | 6. ELECTRICAL PARTS LIST 7. DISASSEMBLY   |    |

|------------------------------------------------------------|-------------------------------------------|----|

| 3. PACKING15                                               | 8. SERVISE MODE                           | 87 |

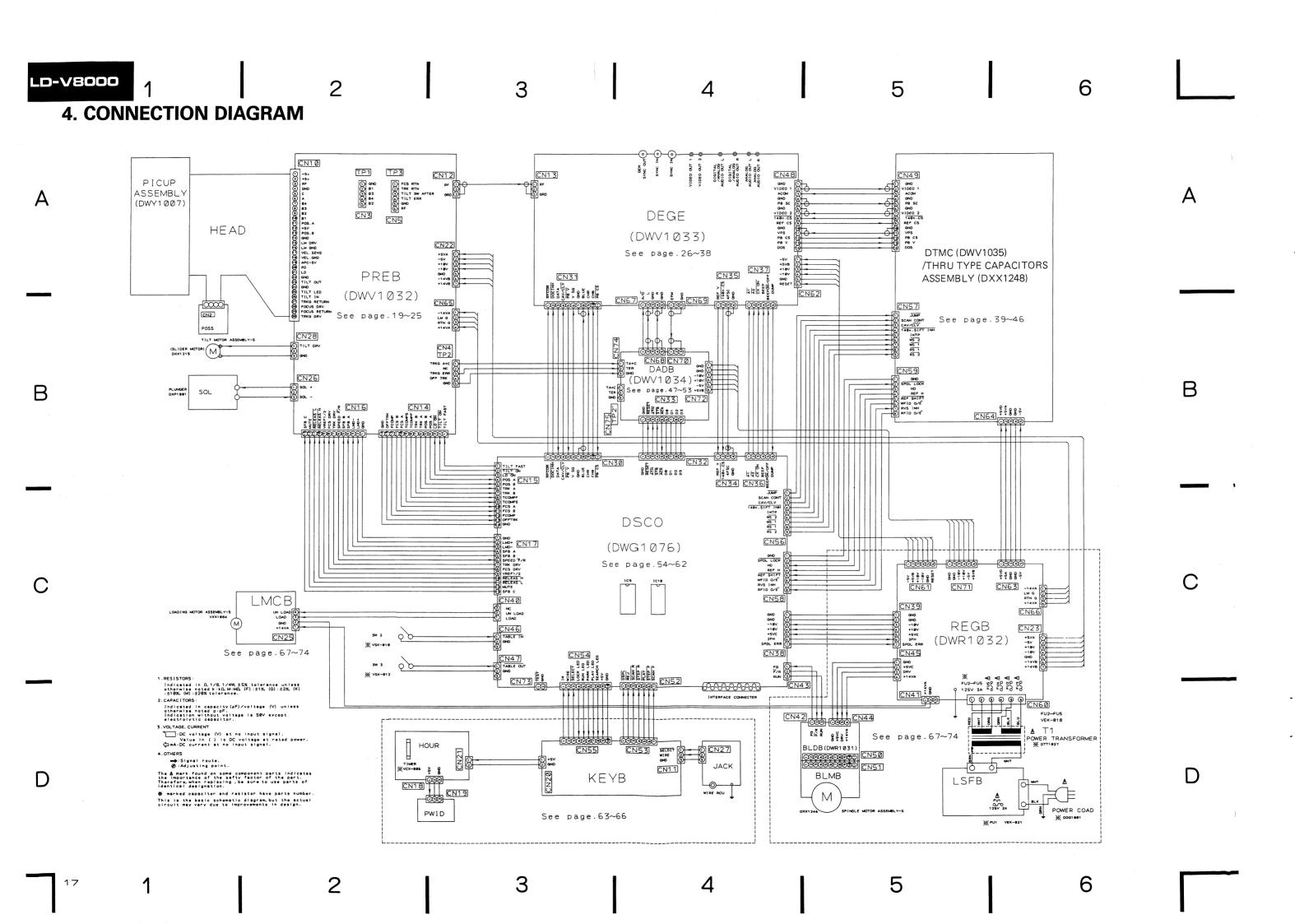

| 4. CONNECTION DIAGRAM17                                    | 9. ADJUSTMENTS<br>10. P.C.BOARDS LOCATION | 88 |

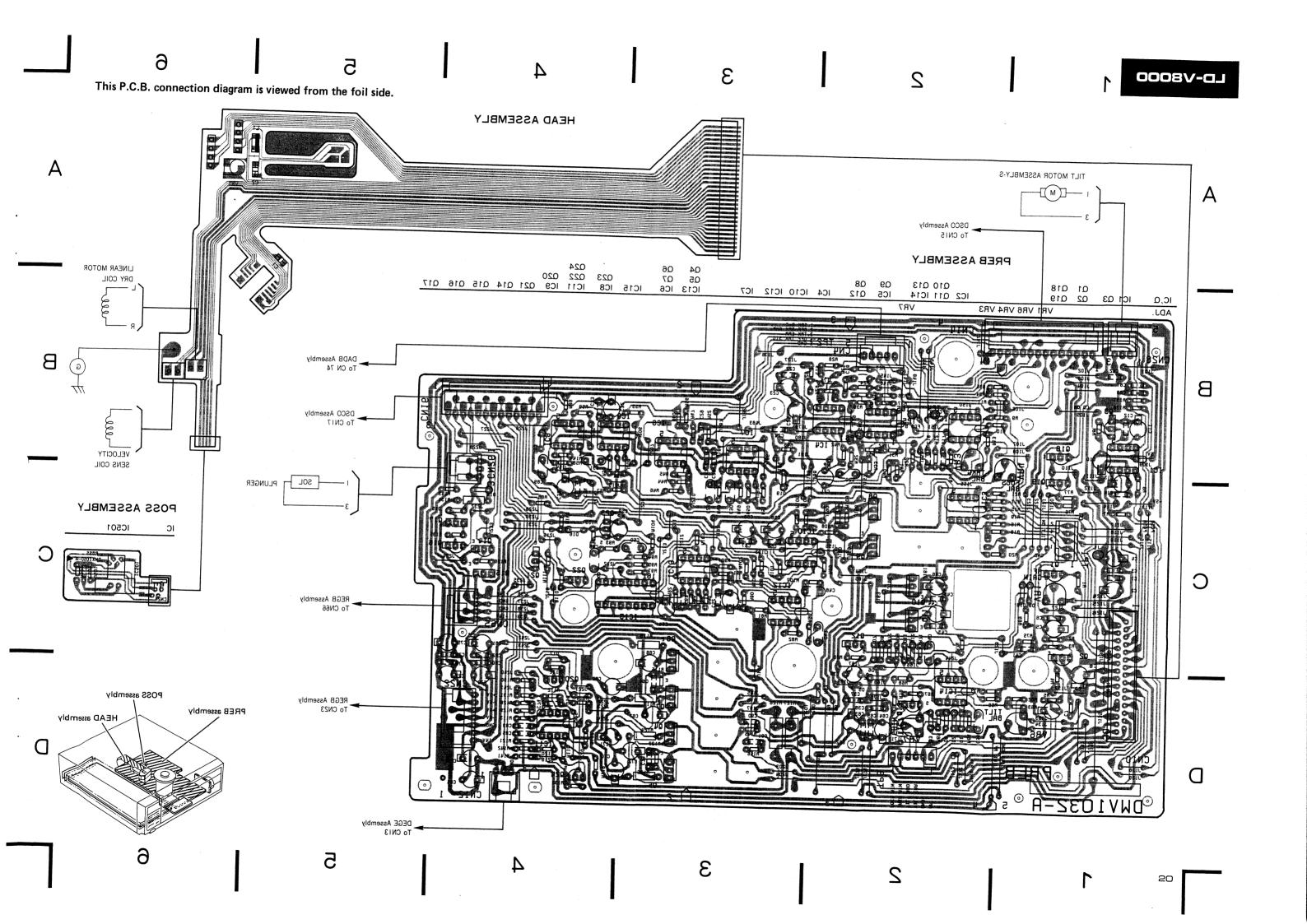

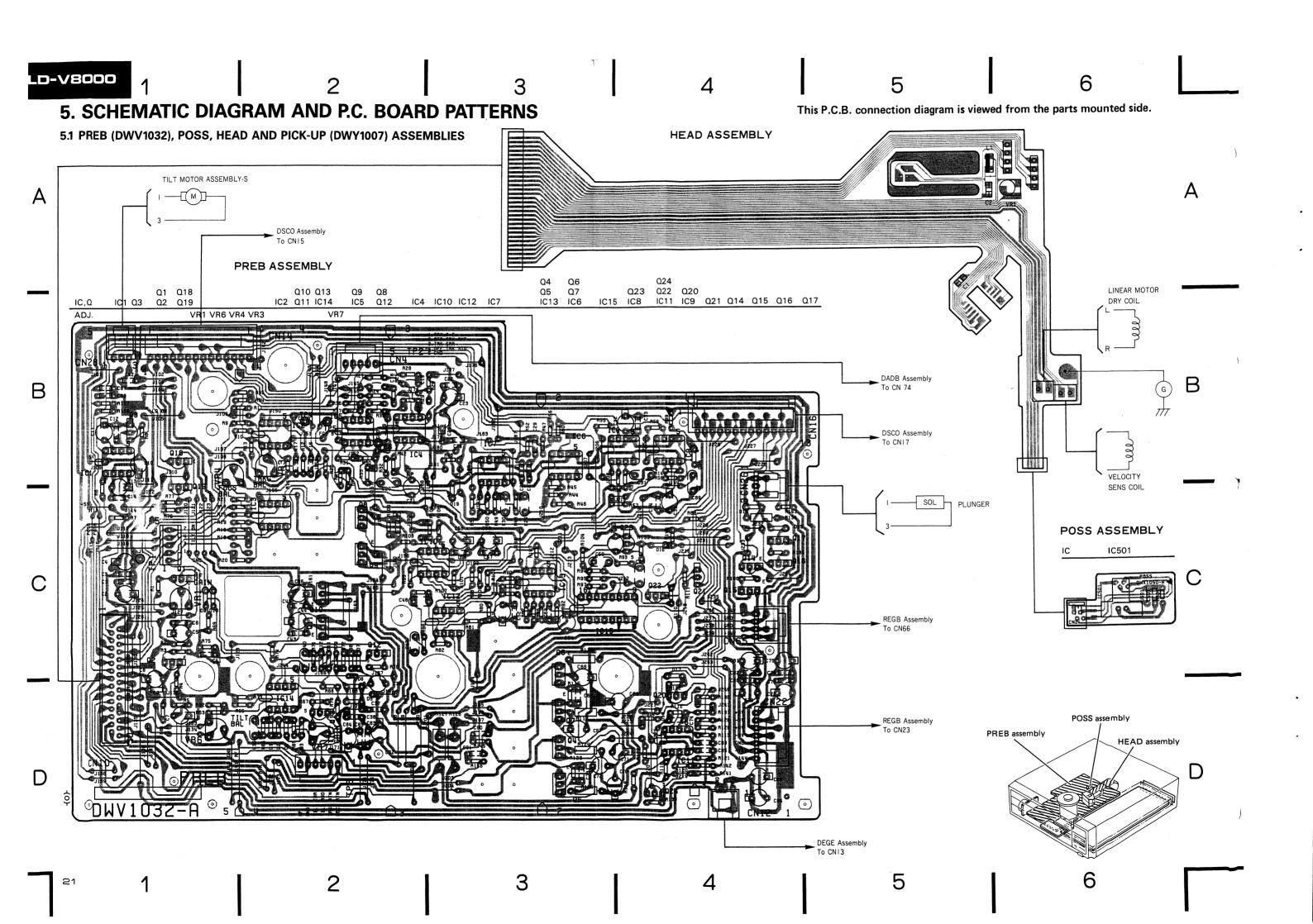

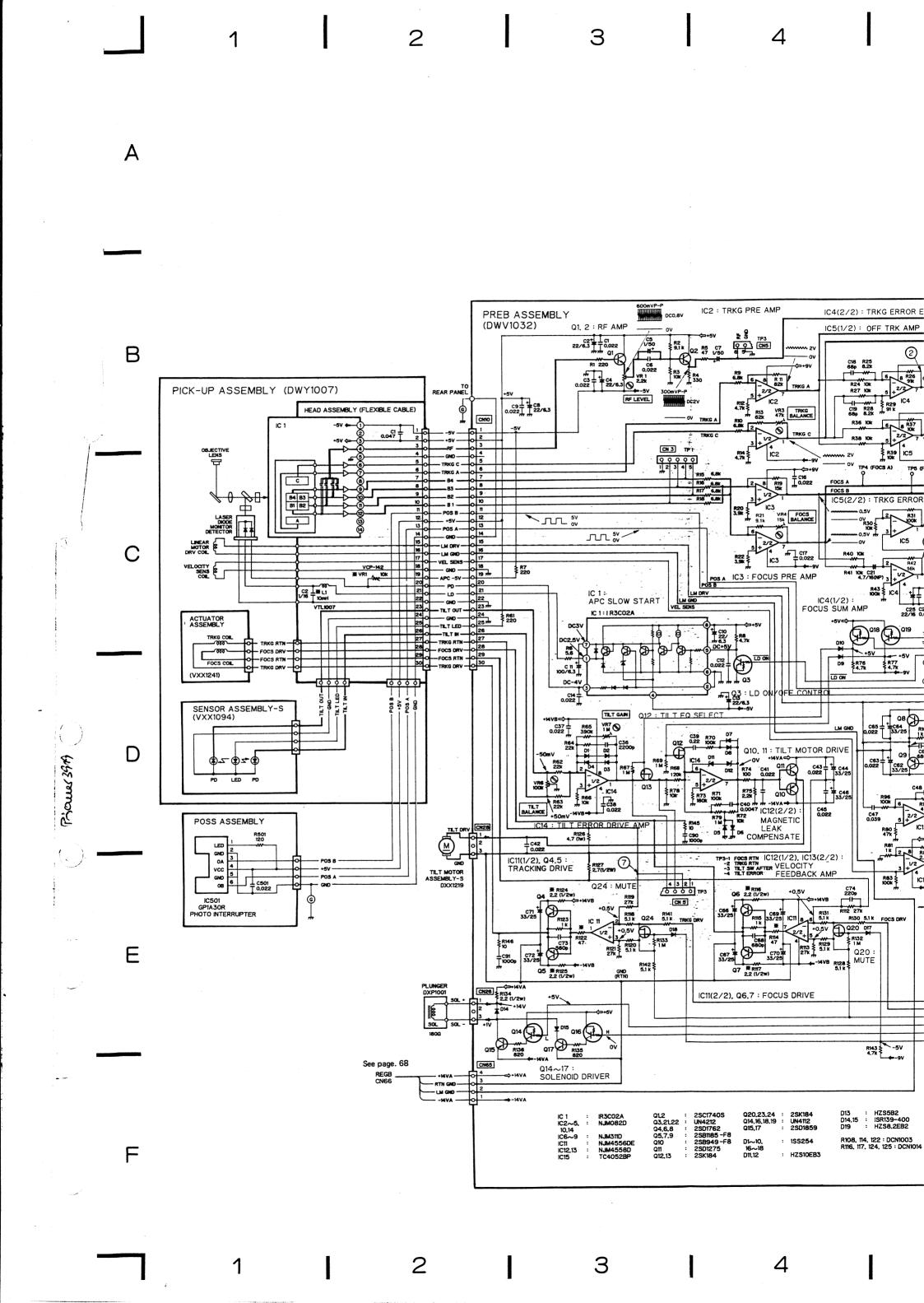

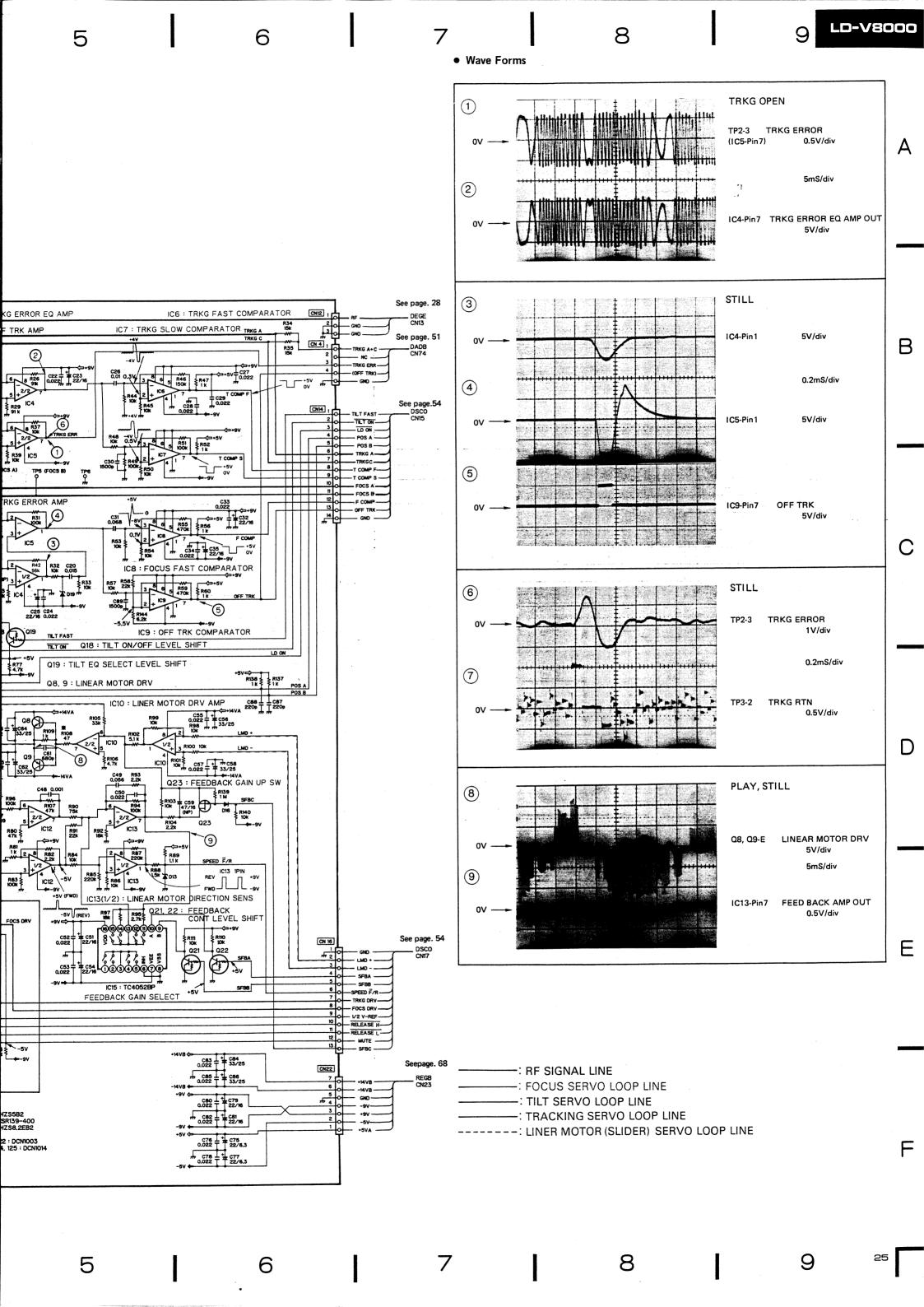

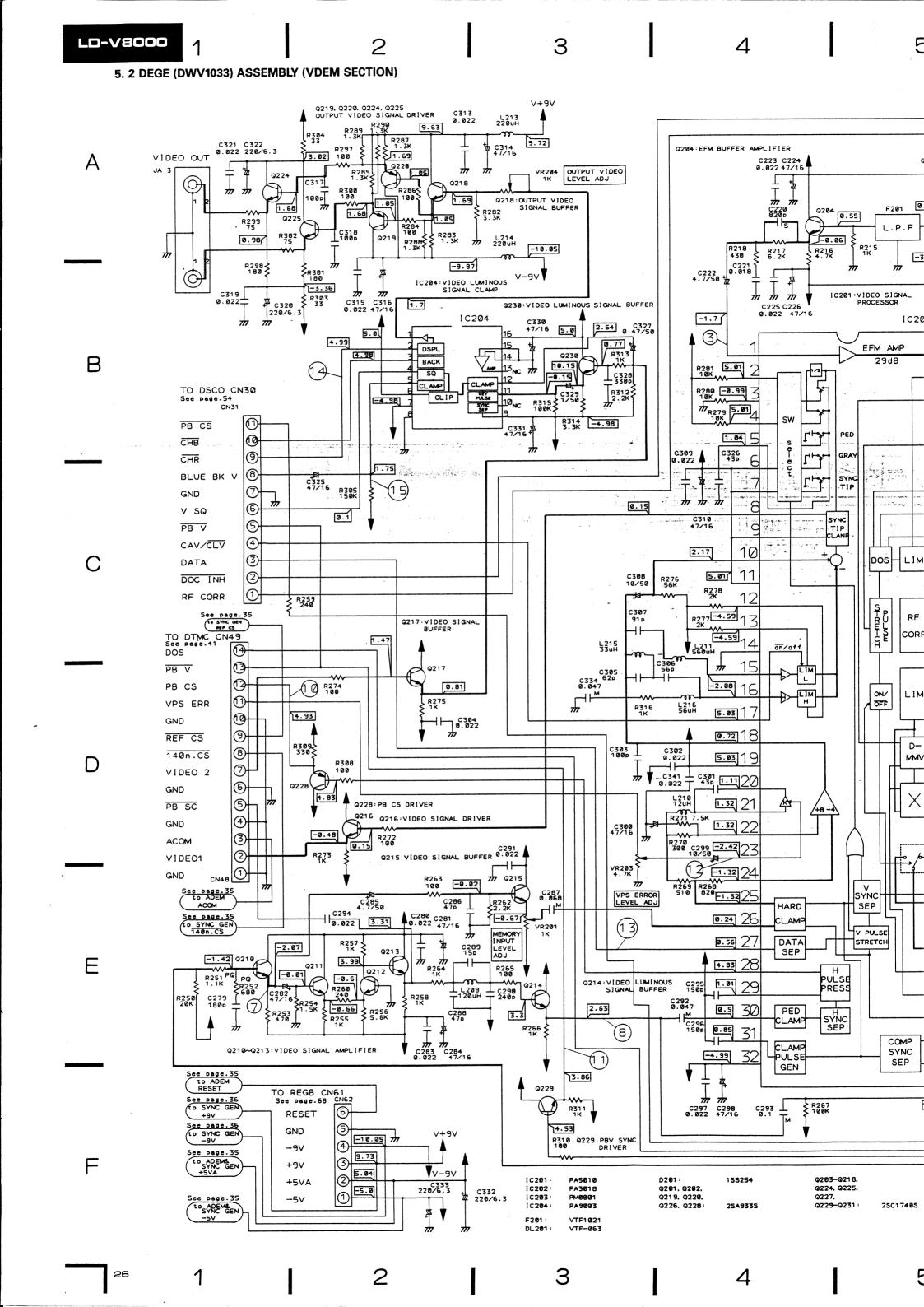

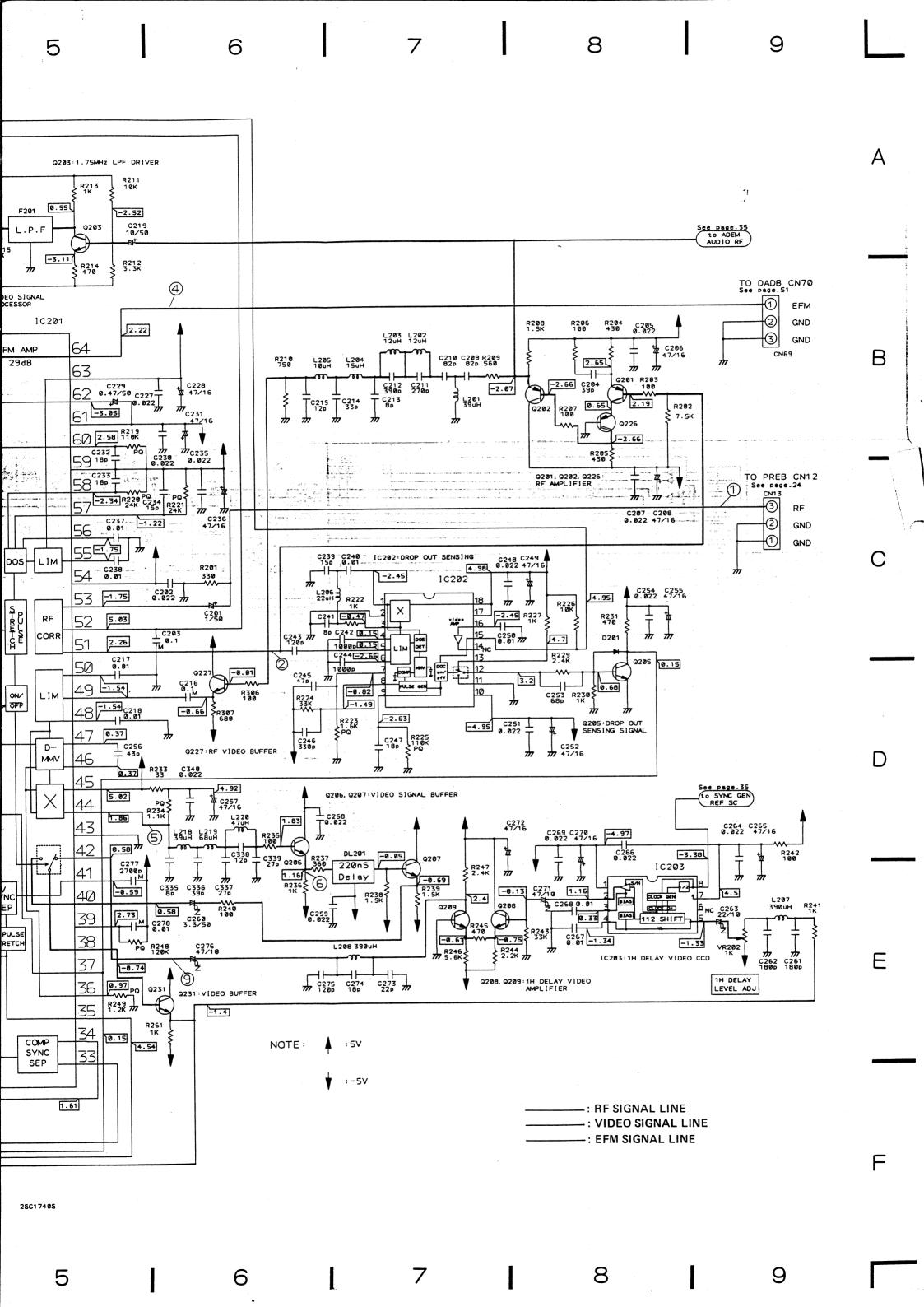

| 5. SCHEMATIC DIAGRAM AND P.C. BOARD PATTERNS21             | 10. P.C.BOARDS LOCATION                   | 12 |

| P.C. BOARD PALLERNS21                                      | 12 SPECIFICATIONS                         | 12 |

#### 1. SAFETY INFORMATION

#### -(FOR USA MODEL ONLY)-

#### 1. SAFETY PRECAUTIONS

The following check should be performed for the continued protection of the customer and service technician.

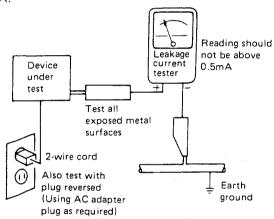

#### LEAKAGE CURRENT CHECK

Measure leakage current to a known earth ground (water pipe, conduit, etc.) by connecting a leakage current tester such as Simpson Model 229-2 or equivalent between the earth ground and all exposed metal parts of the appliance (input/output terminals, screwheads, metal overlays, control shaft, etc.). Plug the AC line cord of the appliance directly into a 120V AC 60Hz outlet and turn the AC power switch on. Any current measured must not exceed 0.5mA.

AC Leakage Test

ANY MEASUREMENTS NOT WITHIN THE LIMITS OUTLINED ABOVE ARE INDICATIVE OF A POTENTIAL SHOCK HAZARD AND MUST BE CORRECTED BEFORE RETURNING THE APPLIANCE TO THE CUSTOMER.

#### 2. PRODUCT SAFETY NOTICE

Many electrical and mechanical parts in the appliance have special safety related characteristics. These are often not evident from visual inspection nor the protection afforded by them necessarily can be obtained by using replacement components rated for voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in this Service Manual.

Electrical components having such features are identified by marking with a  $\triangle$  on the schematics and on the parts list in this Service Manual.

The use of a substitute replacement component which does not have the same safety characteristics as the PIONEER recommended replacement one, shown in the parts list in this Service Manual, may create shock, fire, or other hazards.

Product Safety is continuously under review and new instructions are issued from time to time. For the latest information, always consult the current PIONEER Service Manual. A subscription to, or additional copies of, PIONEER Service Manual may be obtained at a nominal charge from PIONEER.

#### -(FOR EUROPEAN MODEL ONLY)

-VAROITUS!-

LAITE SISÄLTÄÄ LASERDIODIN, JOKA LÄHETTÄÄ NÄKYMÄTÖNTÄ, SILMILLE VAARALLISTA INFRAPUNASÄTEILYÄ LAITTEEN SISÄLLÄ ON LASERDIODIN LÄHEISYYDESSÄ KUVAN 1. MUKAINEN VAROITUSMERKKI.

LASER

Kuva 1

Lasersateilyn

varoitusmerkki

WARNING!-

DEVICE INCLUDES LASER DIODE WHICH EMITS INVISIBLE INFRARED RADIATION WHICH IS DANGEROUS TO EYES. THERE IS A WARNING SIGN ACCORDING TO PICTURE 1 INSIDE THE DEVICE CLOSE TO THE LASER DIODE.

LASER

Picture 1

Warning sign for

laser radiation

ADVERSEL: -

USYNLIG LASERSTRÅLING VED ÅBNING NÅR SIKKERHEDSAFBRYDERE ER UDE AF FUNKTION UNDGÅ UDSAETTELSE FOR STRÅLING.

VIKTIGT-

APARATEN INNEHÅLLER LASER AV HÖGRE KLASS ÄN 1. INGREPP I APPARATEN BÖR GÖRAS AV SPECIELLT UTBILDAD PERSONAL. IMPORTANT

THIS PIONEER APPARATUS CONTAINS LASER OF HIGHER CLASS THAN 1. SERVICING OPERATION OF THE APPARATUS SHOULD BE DONE BY A SPECIALLY INSTRUCTED PERSON.

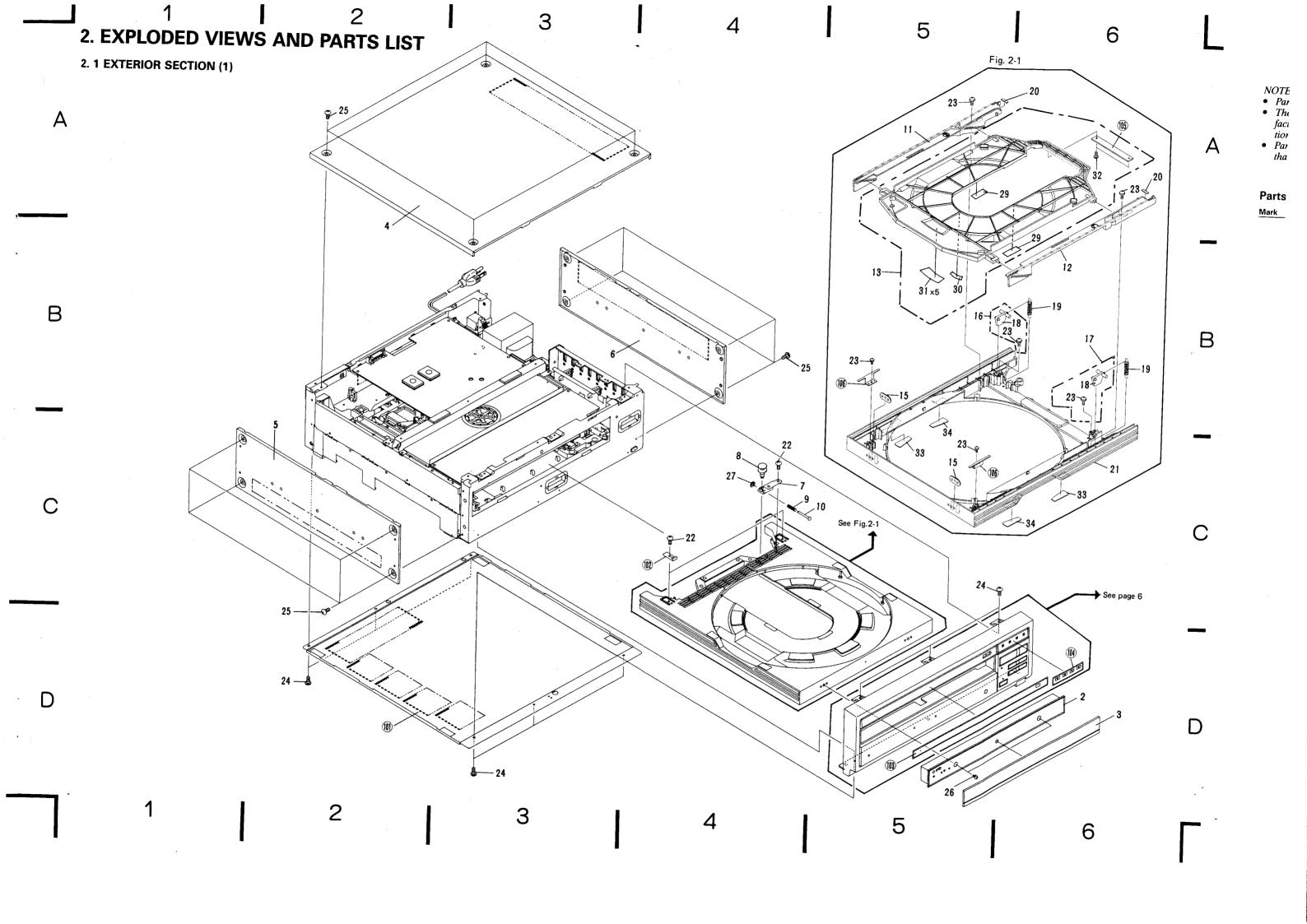

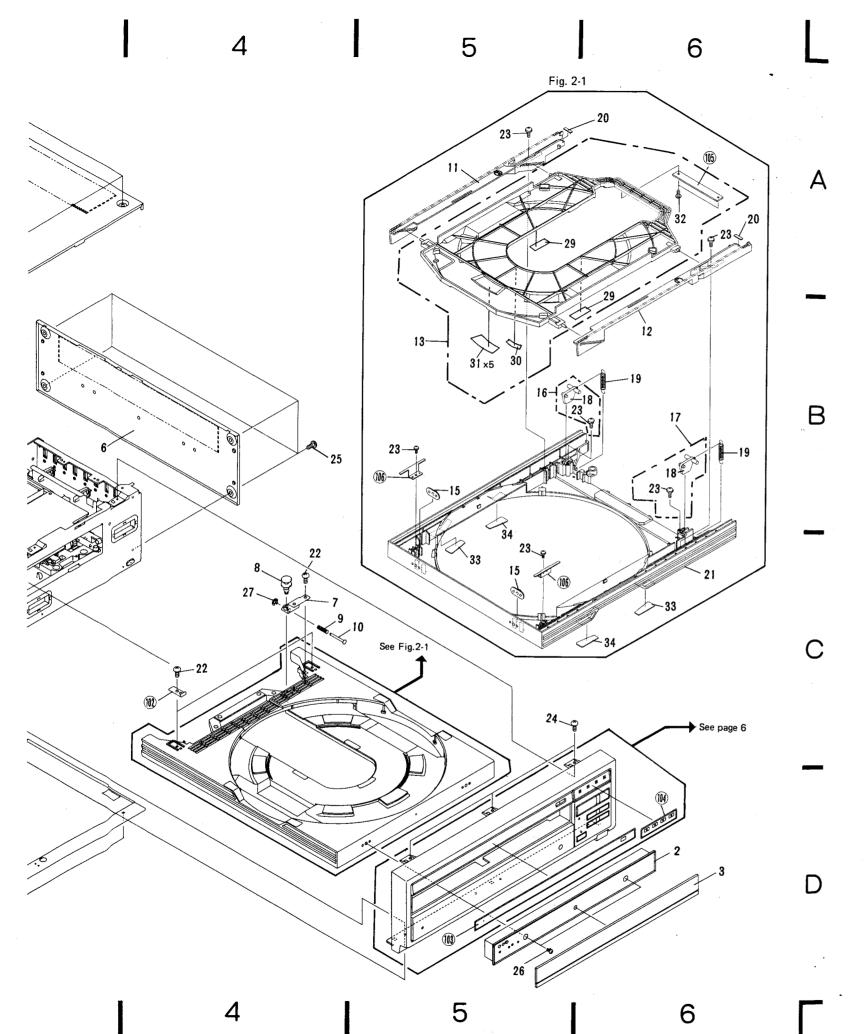

- NOTES:

Parts without part number cannot be supplied.

The △ mark found on some component parts indicates the importance of the safety factor of the part. Therefore, when replacing, be sure to use parts of identical designation.

- tion.

Parts marked by "®" are not always kept in stock. Their delivery time may be longer than usual or they may be unavailable.

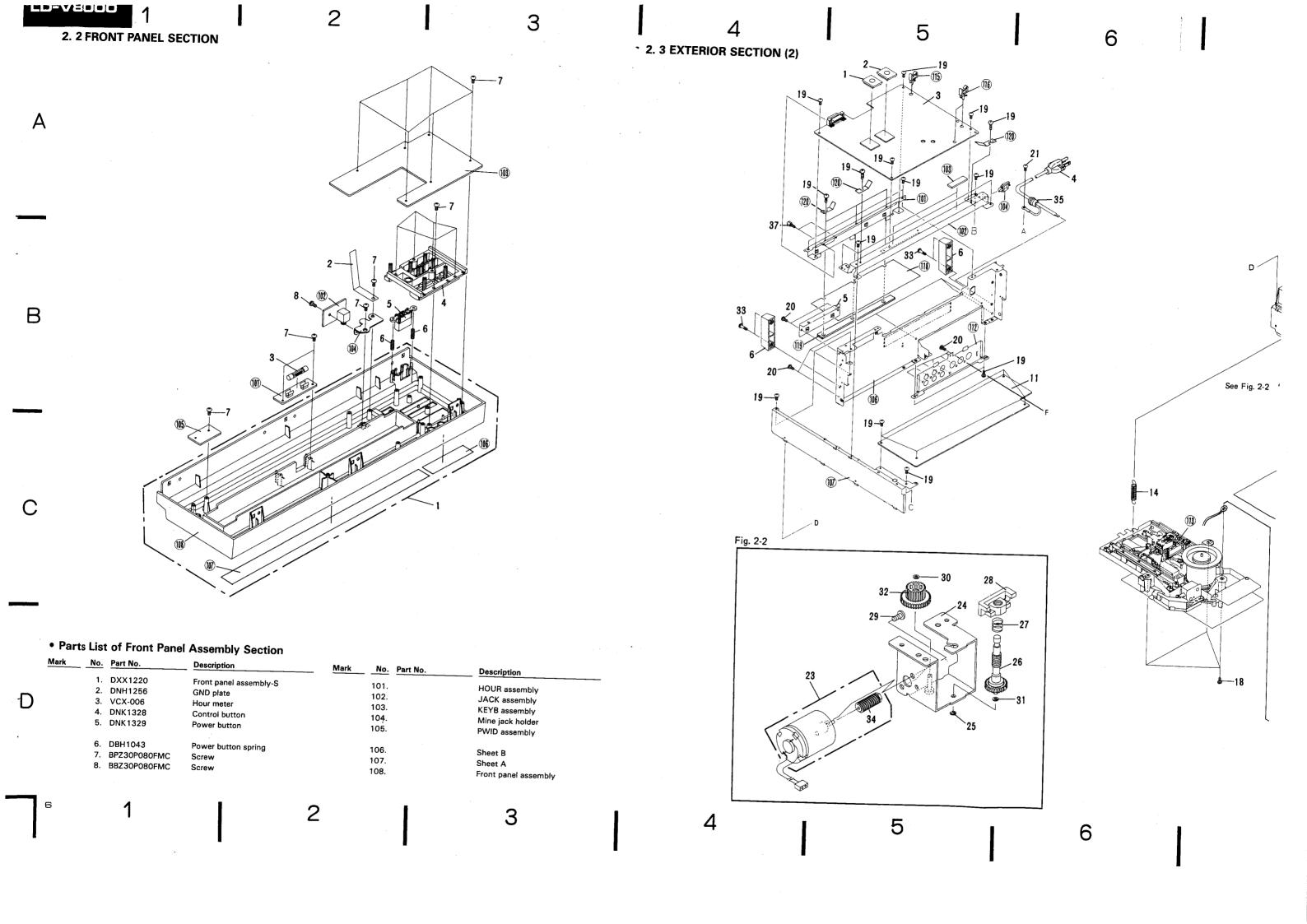

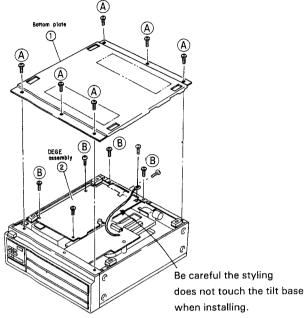

### Parts List of Exterior Section (1)

| Mark | No. | Part No.     | Description          | Mark | No.  | Part No. | Description     |

|------|-----|--------------|----------------------|------|------|----------|-----------------|

|      | 1.  |              |                      |      | 101. |          | Bottom panel    |

|      |     | DNK1159      | Loading panel        |      | 101. |          | Stop plate      |

|      | 3.  | DNK1330      | Decoration panel     |      | 103. |          | Sheet A         |

|      | 4.  | DNE1057      | Top plate            |      | 104. |          | Sheet B         |

|      | 5.  | DNE1066      | Side panel           |      | 105. |          | Reinforce plate |

|      |     |              | 2.22 (2              |      | 100. |          | Heimorce plate  |

|      | 6.  | DNE1058      | Side panel (L)       |      | 106. |          | Rack holder     |

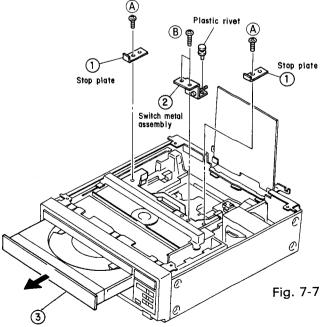

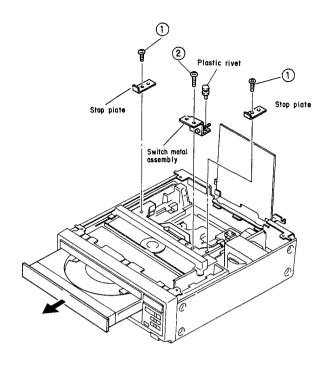

|      | 7.  | DXB1100      | SW metal assembly    |      |      |          |                 |

|      | 8.  | VEC1059      | Prastic rivet        |      |      |          |                 |

|      | 9.  | DBH1039      | Spring               |      |      |          |                 |

|      | 10. | DLA1155      | SW shaft             |      |      |          |                 |

|      | 11. | VNL1061      | Rack gear (R)        |      |      |          |                 |

|      | 12. | VNL1060      | Rack gear (L)        |      |      |          |                 |

|      |     | DXA1118      | Container assembly   |      |      |          |                 |

|      | 14. |              |                      |      |      |          |                 |

|      | 15. | VBN-005      | Nut                  |      |      |          |                 |

|      | 16. | DXB1102      | Stopper (R) assembly |      |      |          |                 |

|      | 17. | DXB1101      | Stopper (L) assembly |      |      |          |                 |

|      | 18. | VNL1062      | Stopper              |      |      |          |                 |

|      | 19. | VBH1021      | Stopper spring       |      |      |          |                 |

|      | 20. | VEB1041      | Rack dump rubber     |      |      |          |                 |

|      |     | DXA1117      | Carry assembly       |      |      |          |                 |

|      |     | BPZ30P080FCU | Screw                |      |      |          |                 |

|      |     | IPZ30P080FCU | Screw                |      |      |          |                 |

|      |     | BBZ30P080FMC | Screw                |      |      |          |                 |

|      | 25. | FBT40P080FZK | Screw                |      |      |          |                 |

|      | 26. | PMA40P100FMC | Screw                |      |      |          |                 |

|      |     | YE20FUC      | E-ring               |      |      |          |                 |

|      | 28. |              |                      |      |      |          |                 |

|      | 29. | DED1031      | Disc pad B           |      |      |          |                 |

|      | 30. | DED1030      | Disc pad A           |      |      |          |                 |

|      |     | DED1032      | Disc pad C           |      |      |          |                 |

|      |     | BPZ30P060FMC | Screw                |      |      |          |                 |

|      |     | DED1033      | Disc pad D           |      |      |          |                 |

|      | 34. | DED1034      | Disc pad E           |      |      |          |                 |

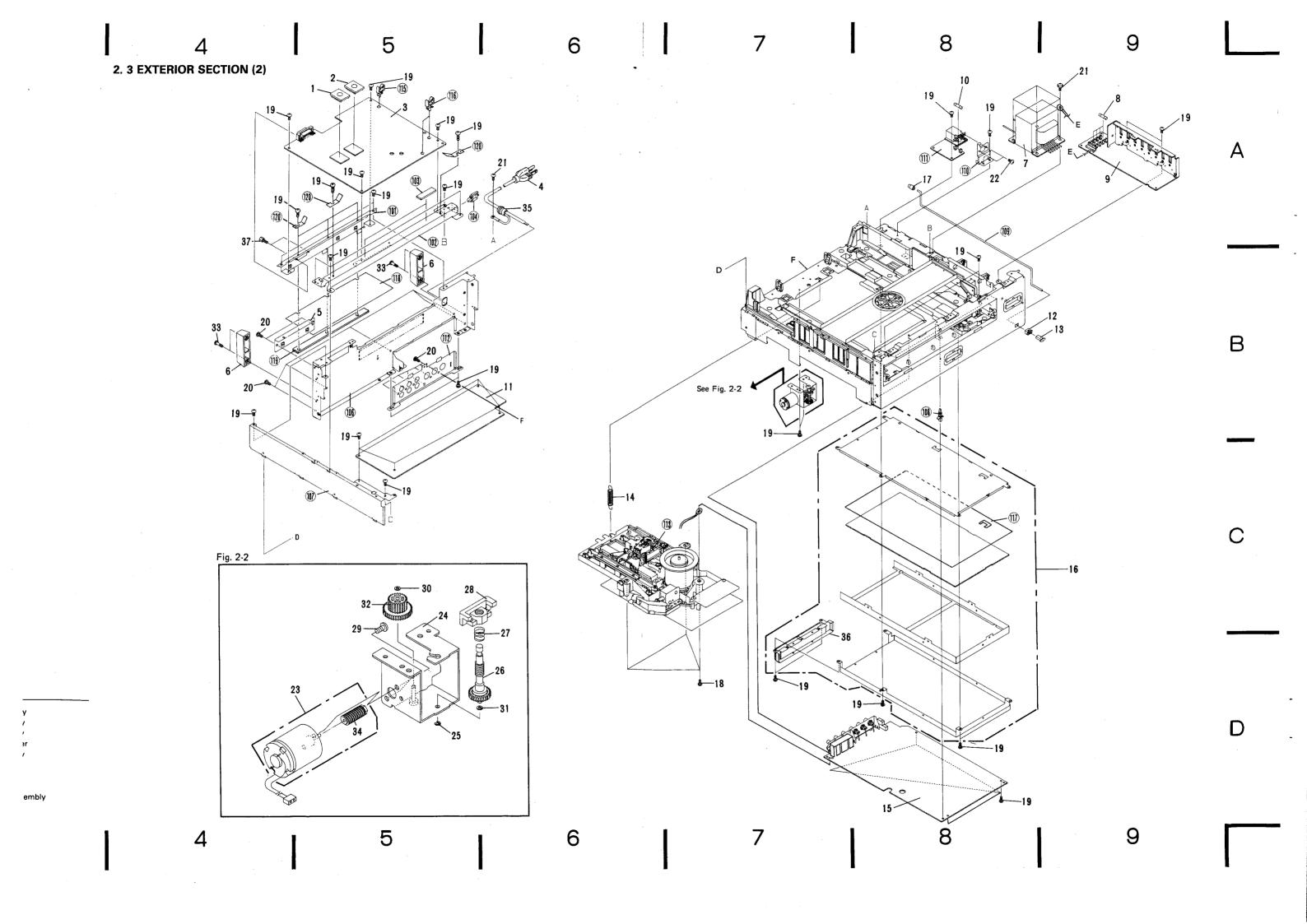

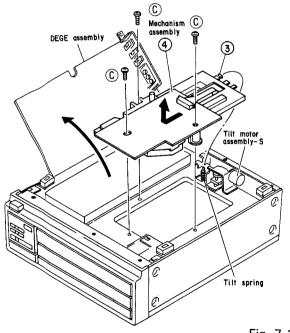

# Parts List of Exterior Section (2)

| Mark     | No. | Part No.     | Description                   | Mark | No. | Part No. | Description        |

|----------|-----|--------------|-------------------------------|------|-----|----------|--------------------|

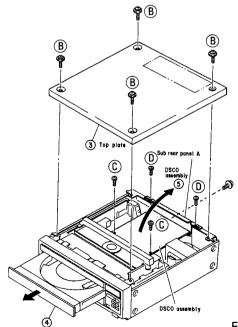

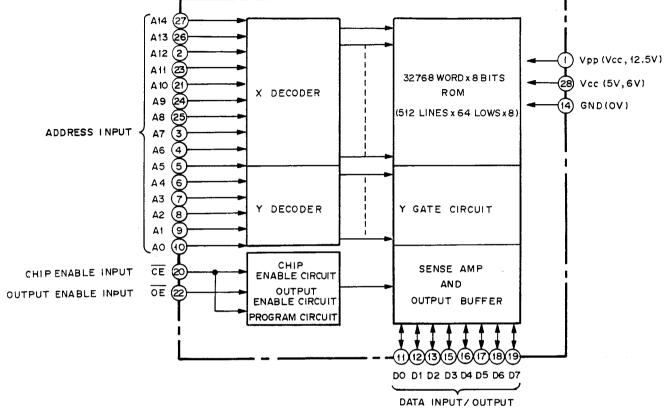

|          | 1.  | DYW1041      | Program EP-ROM (IC9)          | 1    | 01. |          | Sub rear panel (A) |

|          | 2.  | DYW1042      | Program EP-ROM (IC10)         | 1    | 02. |          | Reinforce bridge   |

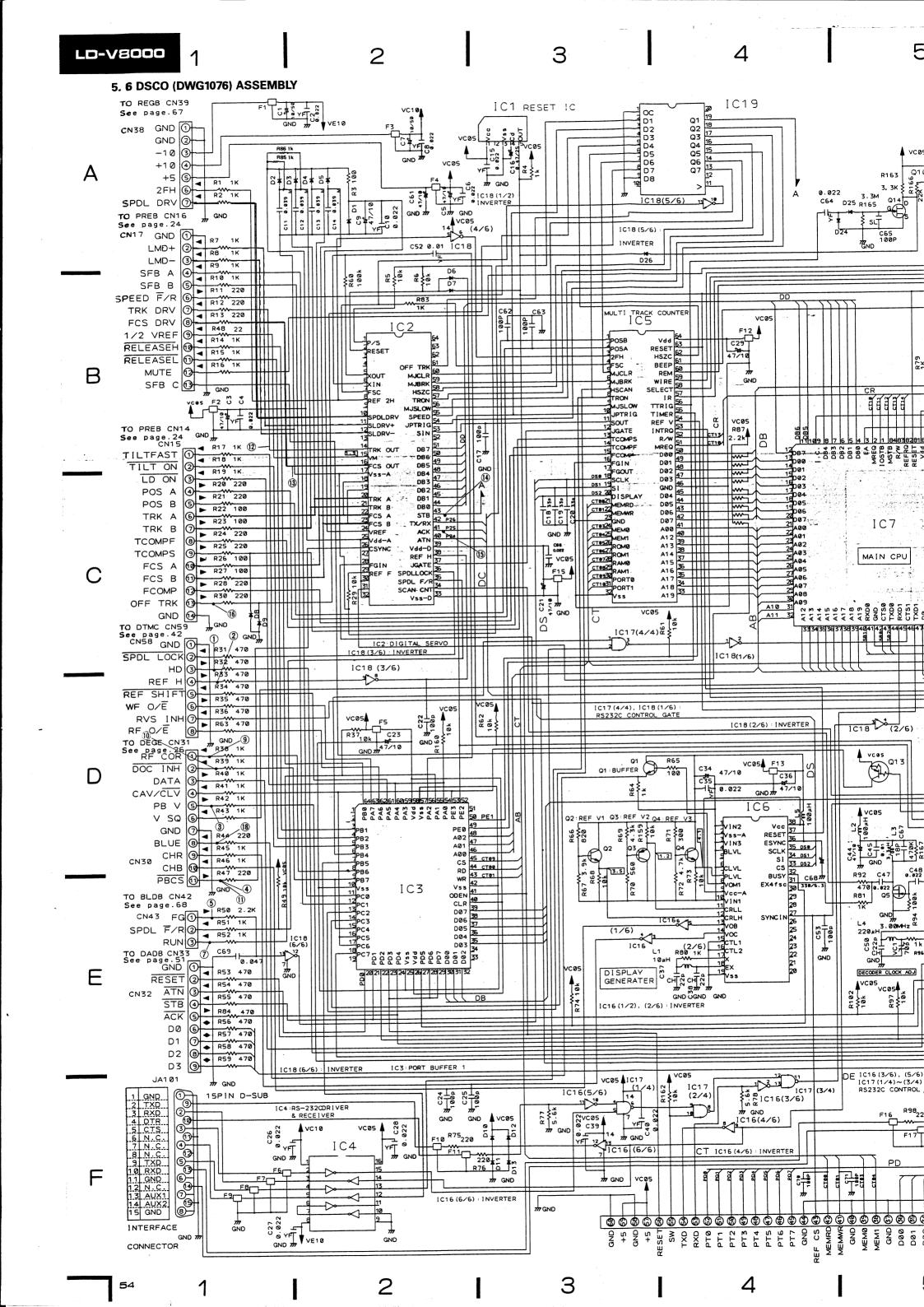

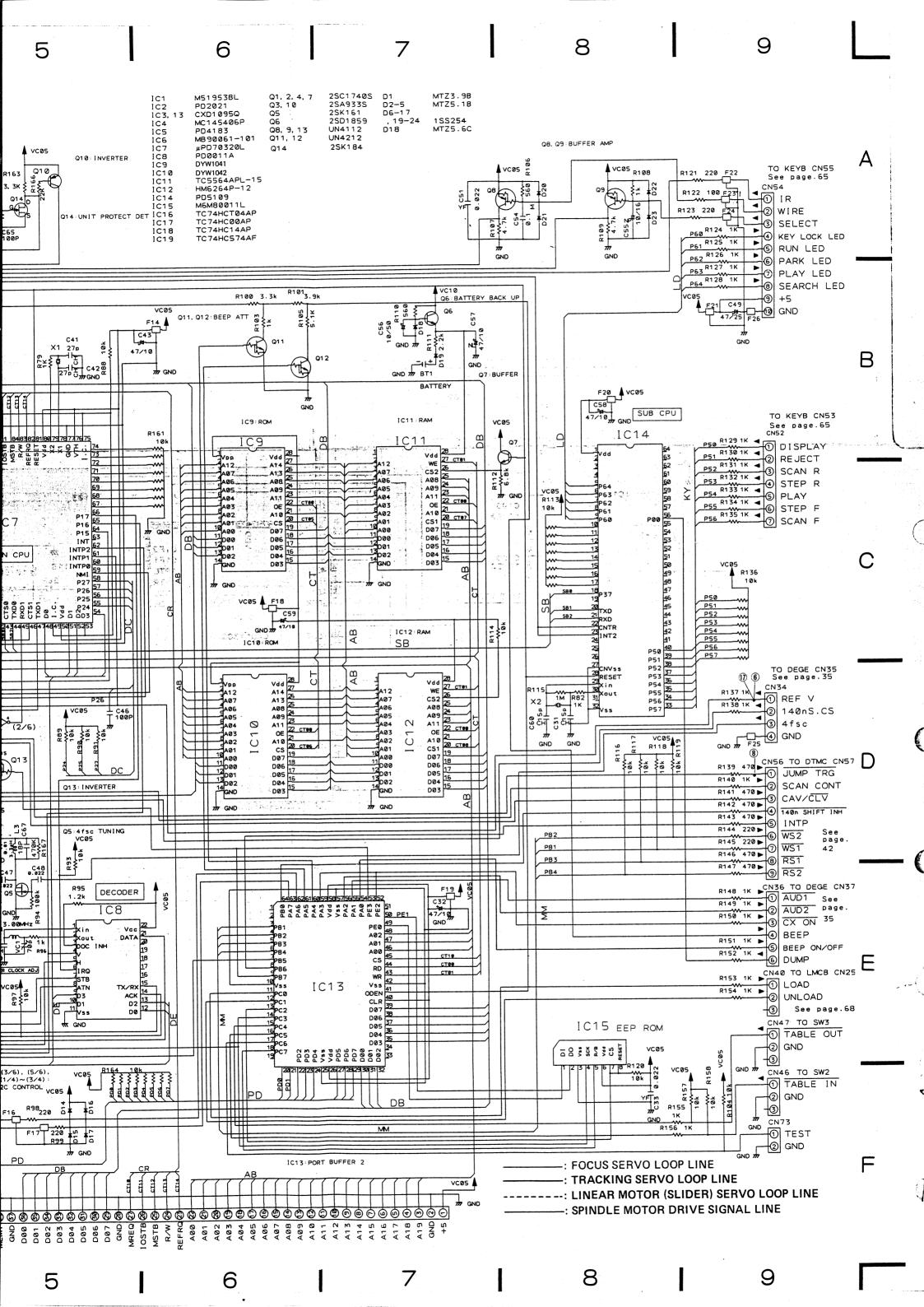

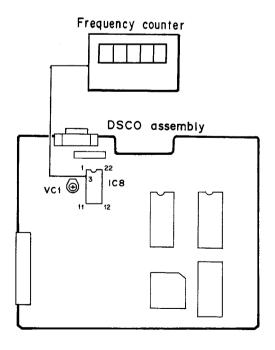

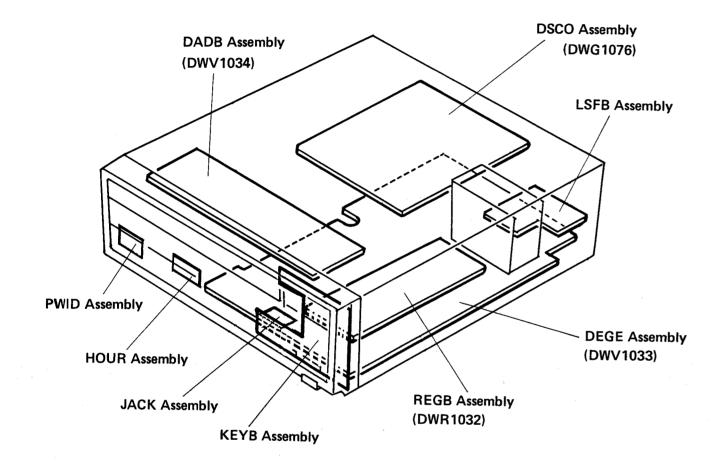

|          | 3.  | DWG1076      | DSCO assembly                 | 1    | 03. |          | Dumper rubber      |

|          | 4.  | DDG1001      | AC power cord                 | 1    | 04. |          | Wire clip          |

|          | 5.  |              | Sub rear panel (C)            | 1    | 05. |          |                    |

|          | -   |              | •                             |      |     |          |                    |

|          | 6.  | VNL-181      | Protector                     | 1    | 06. |          | Rear panel         |

| $\Delta$ | 7.  | DTT1027      | Power transformer (T1)        | 1    | 07. |          | Reinforce plate    |

| $\Delta$ | 8.  | VEK-018      | Fuse (FU2 — FU5) (3A)         |      | 08. |          | PC support         |

|          | 9.  | DWR1032      | REGB assembly                 |      | 09. |          | PSW joint          |

| Æ        | 10. | VEK-021      | Fuse (FU1)                    | 1    | 10. |          | SW holder          |

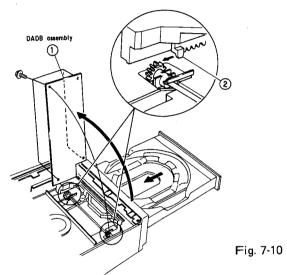

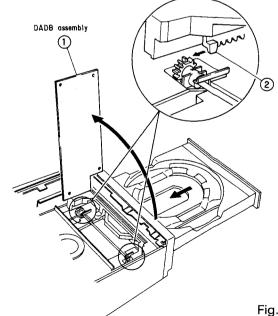

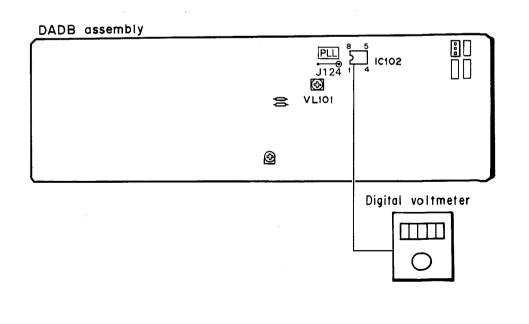

|          | 11. | DWV1034      | DADB assembly                 | 1    | 11. |          | LSFB assembly      |

|          |     | DNK1326      | PSW bush                      | 1    | 12. |          | Sub rear panel (B) |

|          |     | DNK1325      | PSW cap                       | 1    | 13. |          | Mechanism assembly |

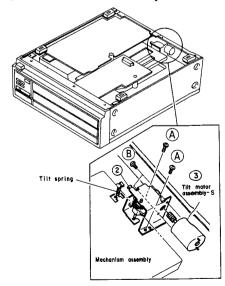

|          | 14. |              | Tilt spring                   | 1    | 14. |          | Connection bolt    |

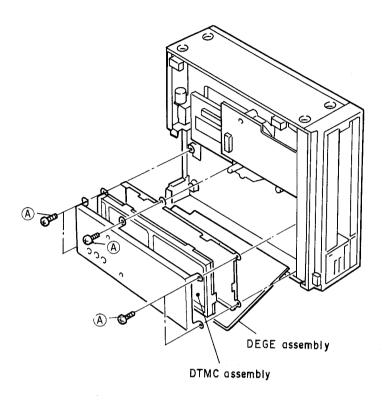

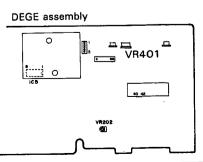

|          | 15. |              | DEGE assembly                 | 1    | 15. |          | Wire clip          |

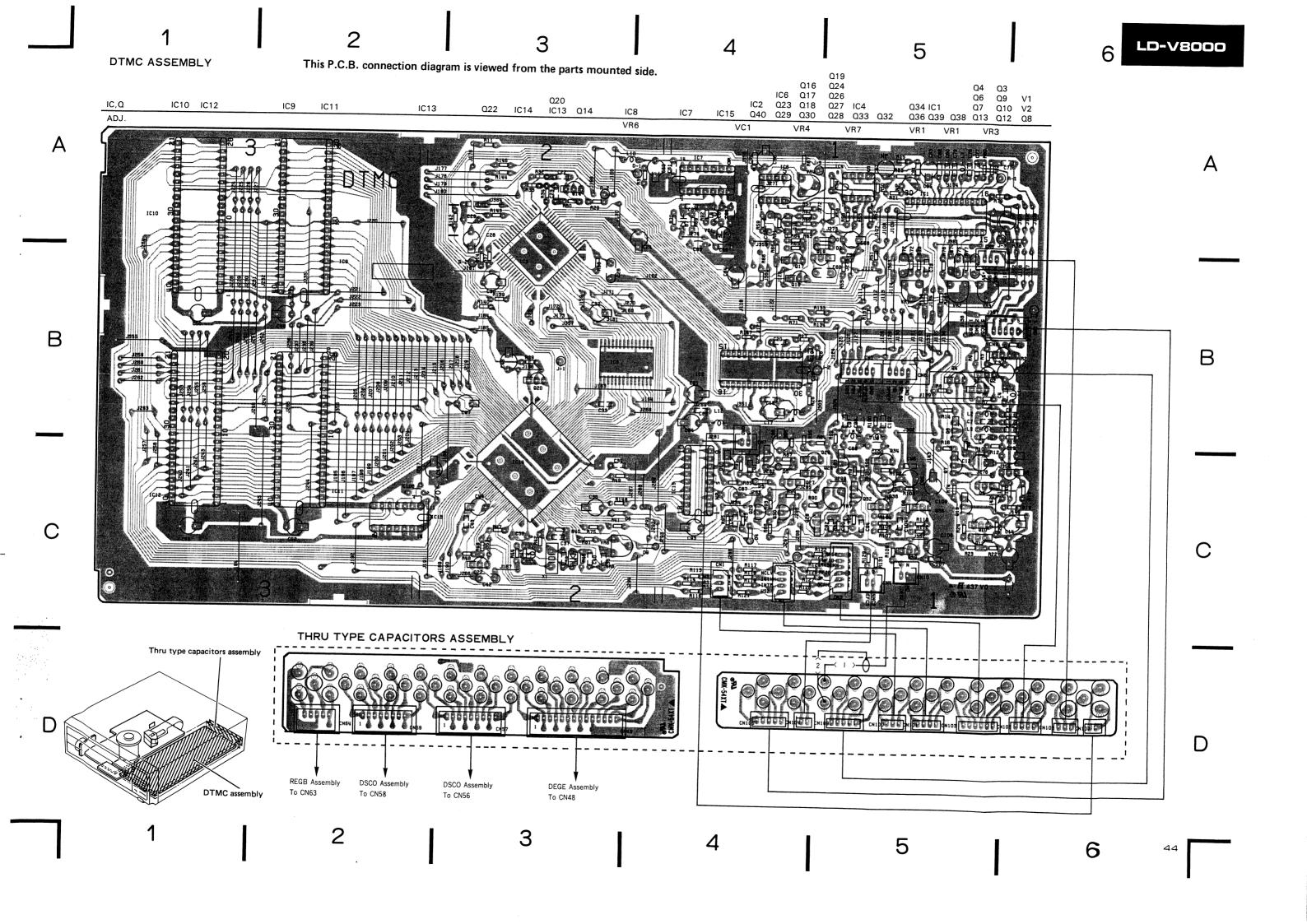

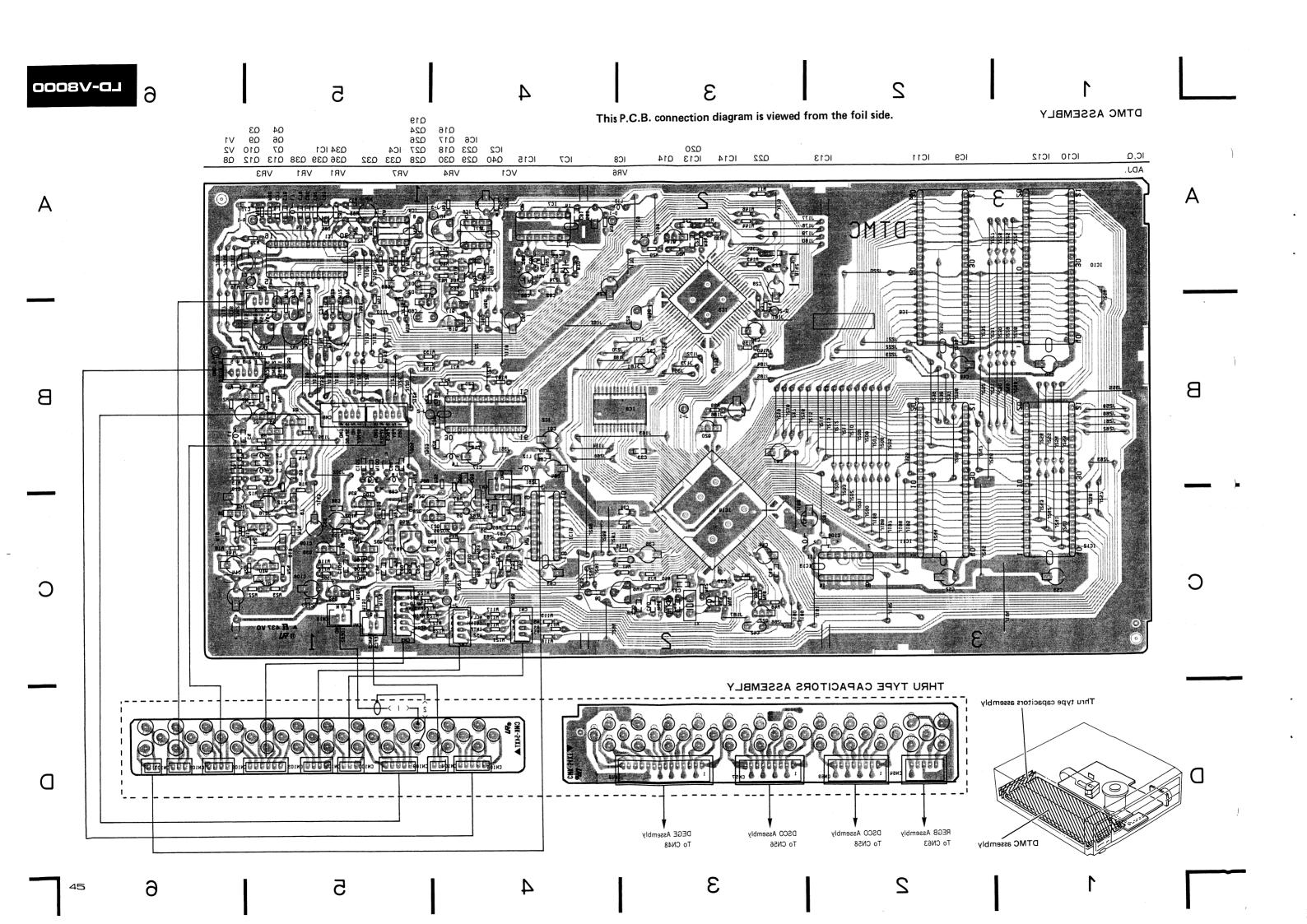

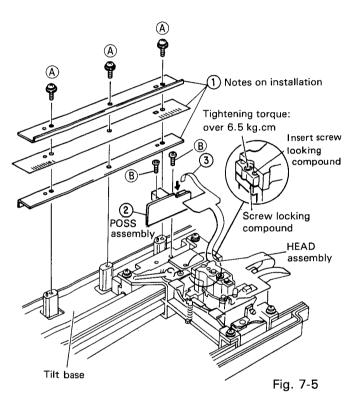

|          | 16  | DWV1035      | DTMC assembly                 | 1    | 16. |          | Wire clip          |

|          | 17. |              | Joint cap                     |      | 17. |          | Protect sheet      |

|          | 18. |              | Screw                         | 1    | 18. |          | Shield sheet       |

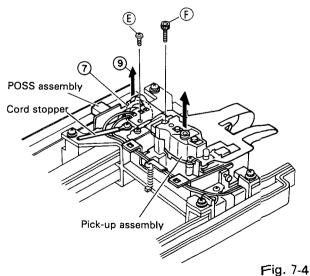

|          |     | BBZ30P080FMC | Screw                         | 1    | 19. |          | Shield plate       |

|          | 20. |              | Screw                         | 1    | 20. |          | Earth rag          |

|          | 21. | PMZ40P080FMC | Screw                         |      |     |          |                    |

|          |     | PMZ30P060FMC | Screw                         |      |     |          |                    |

|          |     | DXX1219      | Tilt motor assembly-S         |      |     |          |                    |

|          | 24. | DXB1114      | Tilt gear base assembly       |      |     |          |                    |

|          |     | YE20FUC      | E-ring                        |      |     |          |                    |

|          | 26  | DXB1118      | Tilt shaft assembly           |      |     |          |                    |

|          | 27. |              | Limit spring                  |      |     |          |                    |

|          | 28. |              | Tilt screw                    |      |     |          |                    |

|          | 29. |              | Screw                         |      |     |          |                    |

|          |     | WT21D040D050 | Washer                        |      |     |          |                    |

|          | 31  | WA31D050D050 | Washer                        |      |     |          |                    |

|          | 32. |              | Transmit gear                 |      |     |          |                    |

|          |     | VCZ30P200FZK | Screw                         |      |     |          |                    |

|          |     | DNK1336      | Tilt worm                     |      |     |          |                    |

|          |     | VEC-201      | Strain relief                 |      |     |          |                    |

|          | 36. | DXX1248      | Thru type capacitors assembly |      |     |          |                    |

|          |     | BBZ30P080FZK | Screw                         |      |     |          |                    |

|          |     |              |                               |      |     |          |                    |

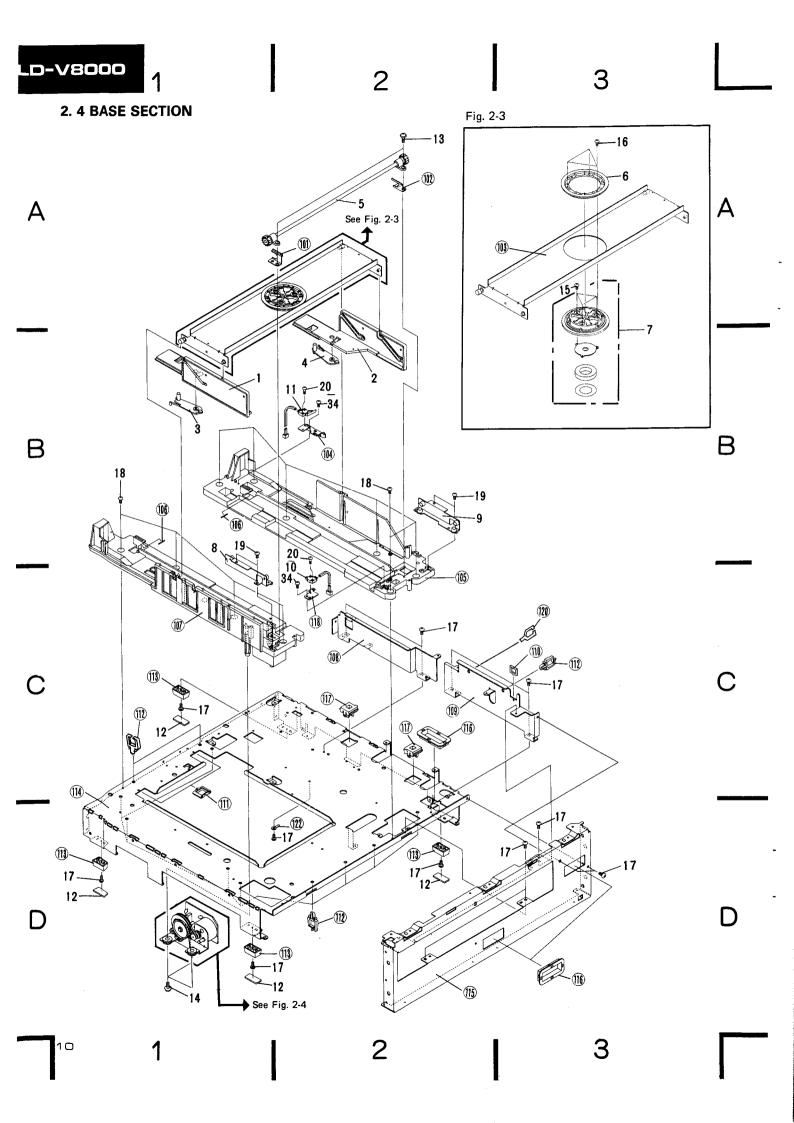

# • Parts List of Base Section

| Mark | No. | Part No.     | Description                   | Mark | No.  | Part No. | Description             |

|------|-----|--------------|-------------------------------|------|------|----------|-------------------------|

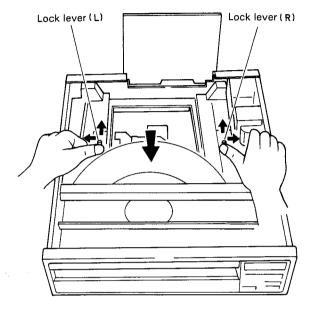

|      | 1.  | VNL1068      | Clamp cam (L)                 |      | 101. |          | Synchronized plate (L)  |

|      | 2.  | VNL1069      | Clamp cam (R)                 |      | 102. |          | Synchronized plate (R)  |

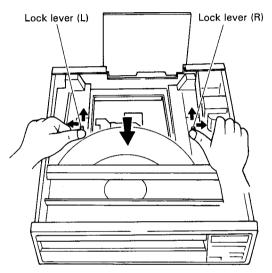

|      |     | VNL1070      | Lock lever (L)                |      | 103. |          | Clamper holder assembly |

|      |     | VNL1071      | Lock lever (R)                |      | 104. |          | SW holder (A)           |

|      | 5.  | DXB1109      | Synchronized gear assembly    |      | 105. |          | Plastic base R          |

|      | 6.  | VNL1130      | Clamper head                  |      | 106. |          | Base clamp rubber       |

|      | 7.  | VXX1157      | Disc clamper assembly-S       |      | 107. |          | Plastic base L          |

|      | 8.  | DXB1106      | Roller plate (L) assembly     |      | 108. |          | Inner plate (R)         |

|      | 9.  | VXA1162      | Roller plate (R) assembly     |      | 109. |          | Inner plate (F)         |

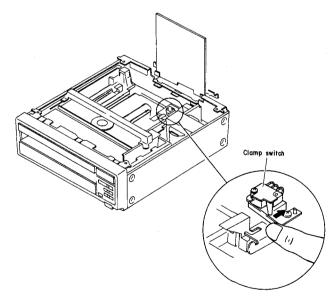

|      | 10. | VSK-012      | Slide switch (TABLE/OUT) (S3) |      | 110. |          | Edge guard              |

|      | 11. | VSK-010      | Slide switch (TABLE/IN) (S2)  |      | 111. |          | Edge guard              |

|      | 12. | DEB1066      | Leg pad                       |      | 112. |          | Wire clip               |

|      | 13. | VBA1002      | Screw                         |      | 113. |          | Reg                     |

|      | 14. | VBA1003      | Screw                         |      | 114. |          | Chassis base            |

|      | 15. | CMZ20P050FMC | Screw                         |      | 115. |          | Front plate             |

|      | 16. | BPZ26P060FCU | Screw                         |      | 116. |          | Protector               |

|      | 17. | BBZ30P080FMC | Screw                         |      | 117. |          |                         |

|      | 18. | ABZ30P080FMC | Screw                         |      | 118. |          | SW holder (B)           |

|      | 19. | BPZ30P080FCU | Screw                         |      | 119. |          | LMCB assembly           |

|      | 20. | BMZ20P080FCU | Screw                         |      | 120. |          | Wire clip               |

|      | 21. | VNL1020      | Gear (A)                      |      | 121. |          | Wire clip               |

|      | 22. | VLL1037      | Gear (A) shaft                |      | 122. |          | Cord stopper plate      |

|      | 23. | WT32D060D050 | Washer                        |      |      |          |                         |

|      |     | VNL1010      | Gear (C)                      |      |      |          |                         |

|      | 25. | VEB1025      | Rubber bushing                |      |      |          |                         |

|      | 26. | VXA1088      | Motor base assembly           |      |      |          |                         |

|      | 27. | VNL1051      | Motor pulley                  |      |      |          |                         |

|      | 28. | VXX1084      | Loading motor assembly-S      |      |      |          |                         |

|      |     | VEC-143      | Plastic rivet                 |      |      |          |                         |

|      | 30. | VEB-125      | Synchronized belt L           |      |      |          |                         |

|      |     | VXA-477      | Pulley (L) assembly           |      |      |          |                         |

|      |     | PMB26P040FMC | Screw                         |      |      |          |                         |

|      | 33. | VNL1064      | Gear (B)                      |      |      |          |                         |

|      |     | BPZ30P080FMC | Screw                         |      |      |          |                         |

|      | 35. | DNK1341      | Rod holder                    |      |      |          |                         |

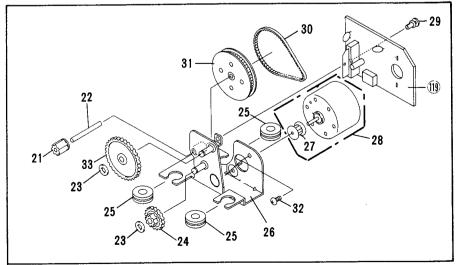

Fig. 2-4

LD-V8000 2 2. 5 MECHANISM ASSEMBLY Α 10--10 17 9 30 30 15 4 33 В В 11-7 29 12 33´ , 16 Fig. 2-5 See Fig. 2-5 -32 - 26 20 29 🕏 12

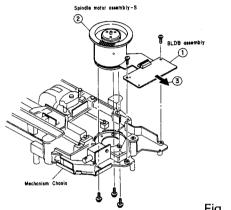

### • Parts List of Mechanism Assembly

| Mark | No.      | Part No.     | Description               |             |      |          | <b>-</b>            |

|------|----------|--------------|---------------------------|-------------|------|----------|---------------------|

|      | 1.       | DXP1005      | Drive unit                | <u>Mark</u> | No.  | Part No. | Description         |

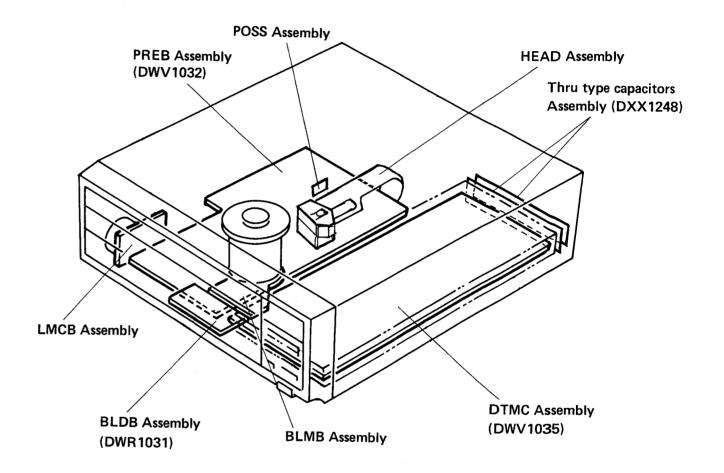

|      | 2.       | DXP1006      | Speed Det. unit           |             | 101. |          | POSS assembly       |

|      | 3.       |              | Shaft catcher             |             | 102. |          | Lock teeth assembly |

|      | 3.<br>4. | DNH1166      | Slit plate                |             | 103. |          | Optical holder      |

|      | 4.<br>5. | DWR1031      | BLDB assembly             |             | 104. |          | Tilt base           |

|      | 5.       | DWN1031      | BEBB assembly             |             | 105. |          | PU holder           |

|      | 6.       | DLA1172      | D shaft                   |             | 106. |          |                     |

|      | 7.       | VLL1107      | Bolt                      |             | 100. |          | • • •               |

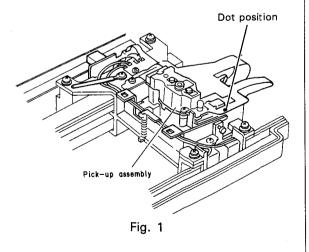

|      | 8.       | DWY1007      | Pick-up assembly          |             | 107. |          | <br>Cord stopper    |

|      | 9.       | DBH1044      | HT spring                 |             | 109. |          | Slider              |

|      | 10.      | DBH1045      | Fixation spring           |             | 110. |          | Reinforce plate     |

|      | 11.      | DBA1013      | Adjustment screw          |             |      |          |                     |

|      | 12.      |              | Roller plate assembly     |             | 111. |          | Mechanism chassis   |

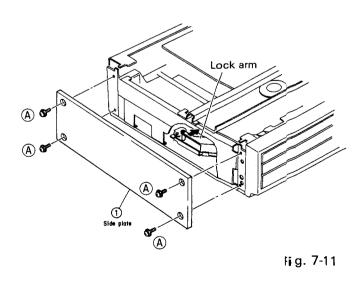

|      |          | DXB1121      | Bearings                  |             | 112. |          | Lock arm assembly   |

|      |          | DXB1111      | Adjustment plate assembly |             | 113. |          | Lock base assembly  |

|      |          | DLA1173      | S shaft                   |             | 114. |          | Plunger base        |

|      | 16       | DEB1053      | Stopper                   |             |      |          |                     |

|      |          | DBH1046      | Lock spring               |             |      |          |                     |

|      |          | DXP1001      | Plunger                   |             |      |          |                     |

|      |          | DNK1333      | Lock cam                  |             |      |          |                     |

|      | 20.      |              | Cam spring                |             |      |          |                     |

|      | 0.4      |              |                           |             |      |          |                     |

|      |          |              | Distanta                  |             |      |          |                     |

|      |          | VNE1103      | Plate                     |             |      |          |                     |

|      |          | DLA1152      | Centering hab             |             |      |          |                     |

|      | 24.      |              | Centering spring          |             |      |          |                     |

|      | 25.      | DEB1052      | Rubber spacer             |             |      |          |                     |

|      | 26.      | DXX1246      | Spindle motor assembly-S  |             |      |          |                     |

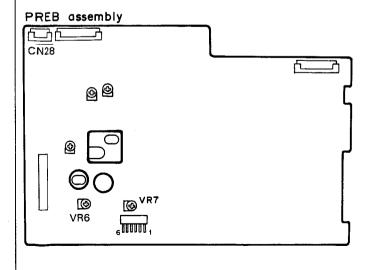

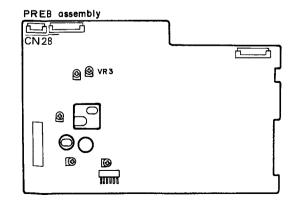

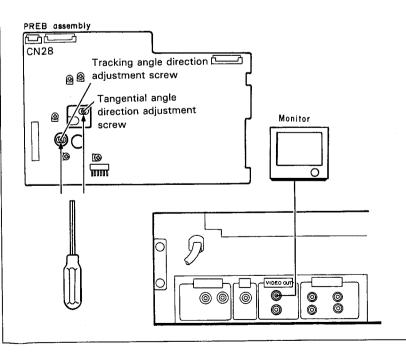

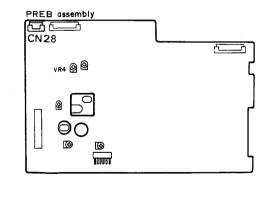

|      | 27.      | DWV1032      | PREB assembly             |             |      |          |                     |

|      | 28.      | WT26D047D050 | Washer                    |             |      |          |                     |

|      | 29.      | PMB30P060FMC | Screw                     |             |      |          |                     |

|      | 30.      | IPZ30P080FMC | Screw                     |             |      |          |                     |

|      | 31.      | BBZ30P080FMC | Screw                     |             |      |          |                     |

|      | 32.      | PMB30P080MC  | Screw                     |             |      |          |                     |

|      | 33.      | PMH30P120FMC | Screw                     |             |      |          |                     |

|      | 34.      | AMZ20P040FMC | Screw                     |             |      |          |                     |

|      |          | PMZ26P040FMC | Screw                     |             |      |          |                     |

|      | 36       | SMZ26H120FZK | Screw                     |             |      |          |                     |

|      | 37.      |              | Screw                     |             |      |          |                     |

|      |          | CBZ30P080FCC | Screw                     |             |      |          |                     |

|      | 39.      | DBK 1024     | G plate (R)               |             |      |          |                     |

|      | 40.      |              | G plate (L)               |             |      |          |                     |

|      |          |              |                           |             |      |          |                     |

В

# 2. 6 PICK-UP ASSEMBLY (DWY1007)

Α

R

C

### • Parts List of Pick-up Assembly

| Mark   | No. | Part No.     | Description            |   |   |   |

|--------|-----|--------------|------------------------|---|---|---|

| _      | 1.  | VXX1241      | Actuator assembly      |   |   |   |

| $\Box$ | 2.  | VXX1094      | Sensor assembly-S      |   |   |   |

|        | 3.  | DXX1247      | Pre pick-up assembly-S |   |   |   |

|        | 4.  | PBZ20P160FMC | Screw                  |   |   |   |

|        | 5.  | PMA20P060FMC | Screw                  |   |   |   |

|        | 6.  | PMA20P080FMC | Screw                  |   |   |   |

|        | 7.  | PMA20P140FMC | Screw                  |   |   |   |

|        | 8.  | PMB20P050FMC | Screw                  |   |   |   |

|        |     |              | •                      |   | _ |   |

| 14     |     | 1            |                        | 2 |   | 3 |

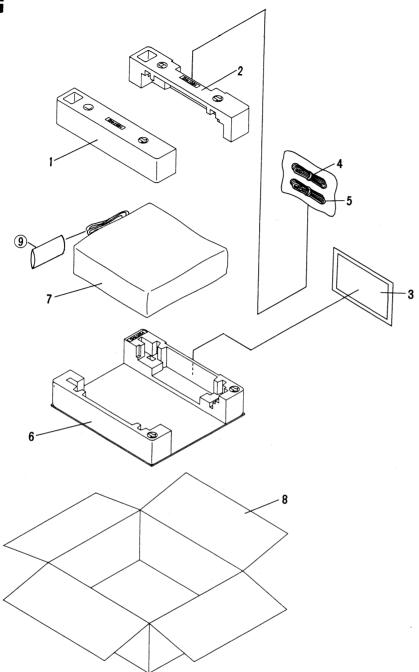

# 3. PACKING

# • Parts List of Packing

| Mark | No.                  | Part No.                      | Description                                                   |

|------|----------------------|-------------------------------|---------------------------------------------------------------|

|      | 1.<br>2.             | DHA 1054<br>DHA 1055          | Top pad L                                                     |

|      | 3.                   | DRB1013                       | Top pad R Operating instructions                              |

|      | 4.<br>5.             | VDE-014<br>VDE-055            | Video cable<br>Connection cord                                |

|      | 6.<br>7.<br>8.<br>9. | DHA1056<br>VHL1005<br>DHG1096 | Bottom pad<br>Packing mat<br>Packing case<br>Polyethylene bag |

# • Notes of P.C. Board Patterns

| P.C.B. pattern diagram indication | Corresponding par<br>symbol                              | t Part name  | P.C.B. pattern diagrar indication | Corresponding part       | Part name                              |  |

|-----------------------------------|----------------------------------------------------------|--------------|-----------------------------------|--------------------------|----------------------------------------|--|

|                                   | or E                                                     | Transistor   | · _ ,                             |                          | Ceramic capacitor                      |  |

| D. S. G                           |                                                          | FET          | $\subset \supset$                 |                          | Mylar capacitor                        |  |

| 040                               |                                                          |              | \$( )                             |                          | Styrol capacitor                       |  |

| <u></u>                           | $\circ \hspace{-1pt} \blacksquare \hspace{-1pt} \bullet$ | Diode        | ₫Z                                | <b>○</b> ₩ • •           | Electrolytic capacitor (Non polarized) |  |

|                                   |                                                          |              | Z                                 |                          | Electrolytic capacitor (Noiseless)     |  |

| a <u>T</u>                        | <b>○</b>                                                 | Zenner diode |                                   | <b>○</b> ‡ + • •         | Electrolytic capacitor (Polarized)     |  |

| 7                                 |                                                          |              |                                   |                          | Electrolytic capacitor (Polarized)     |  |

| 74-                               | · · · · · · · · · · · · · · · · · · ·                    | LED          |                                   | <b>○</b> ── <b> </b>     | Power capacitor                        |  |

|                                   |                                                          | Varactor     |                                   | ·                        | Semi-fixed resistor                    |  |

|                                   | $\sim$                                                   | Tact switch  |                                   |                          | Resistor array                         |  |

|                                   | <b>○ → ○</b>                                             |              |                                   |                          |                                        |  |

| ^                                 | ~~~~                                                     | Inductor     | ~                                 | <b>─</b> ─₩∘             | Resistor                               |  |

|                                   |                                                          | madetor      | 0                                 |                          |                                        |  |

|                                   | ~ <b>~~</b>                                              | Coil         | -IDF                              | <b>○──</b> □ <b>├</b> ─○ | Resonator                              |  |

| 3<br>2<br>1                       |                                                          | Transformer  |                                   | · ~~~                    | Thermistor                             |  |

| 8 1                               |                                                          | Filter       |                                   |                          |                                        |  |

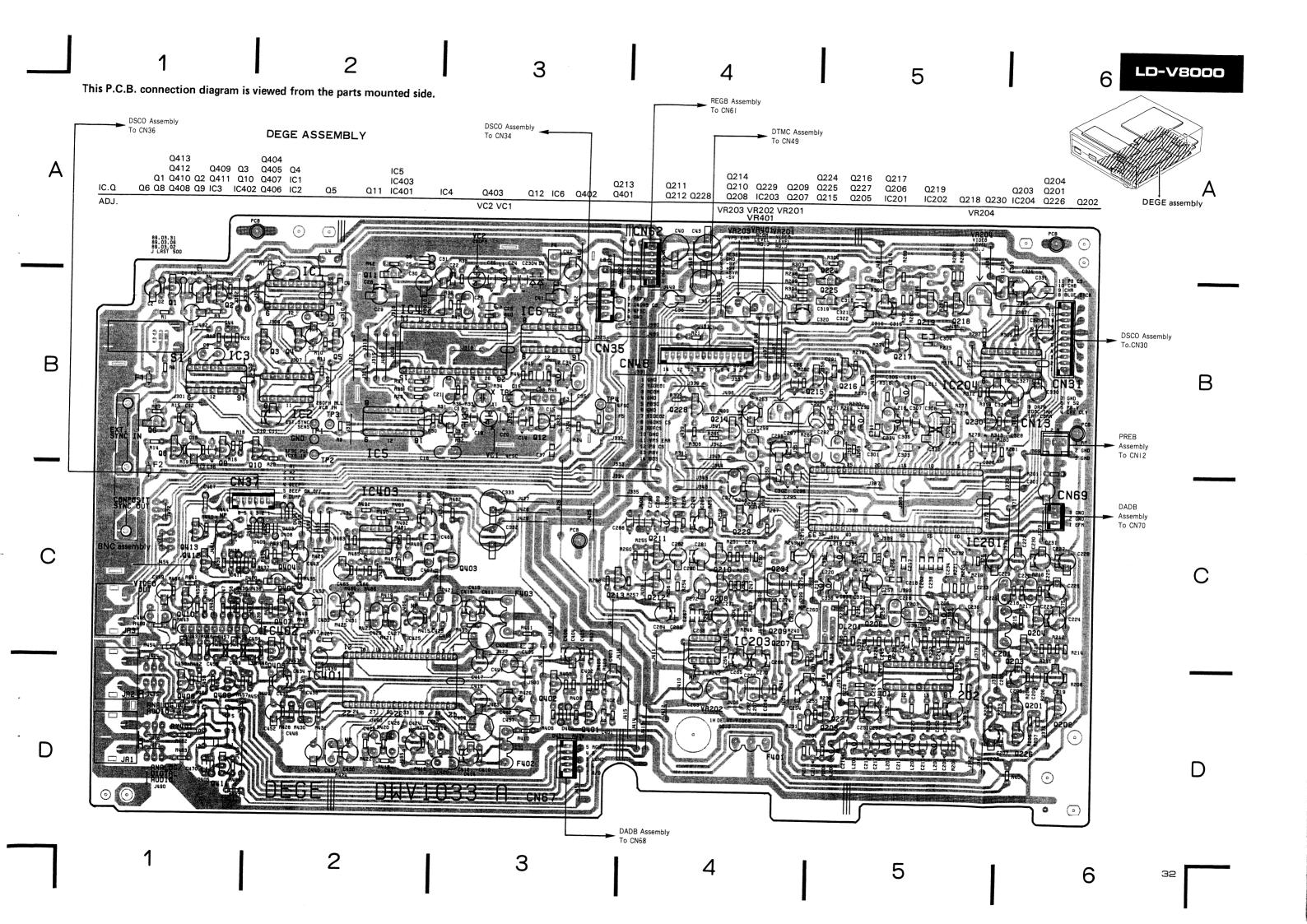

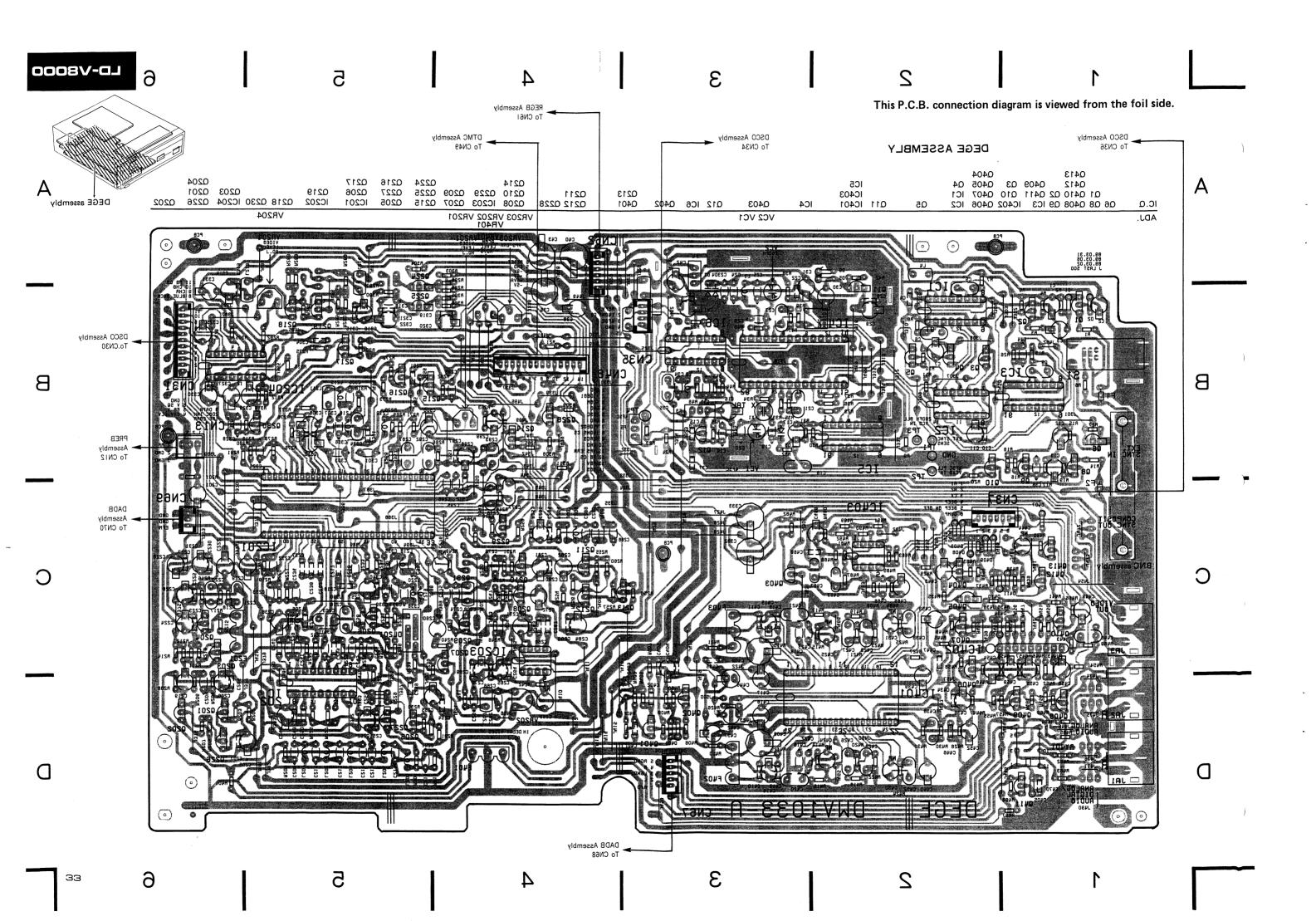

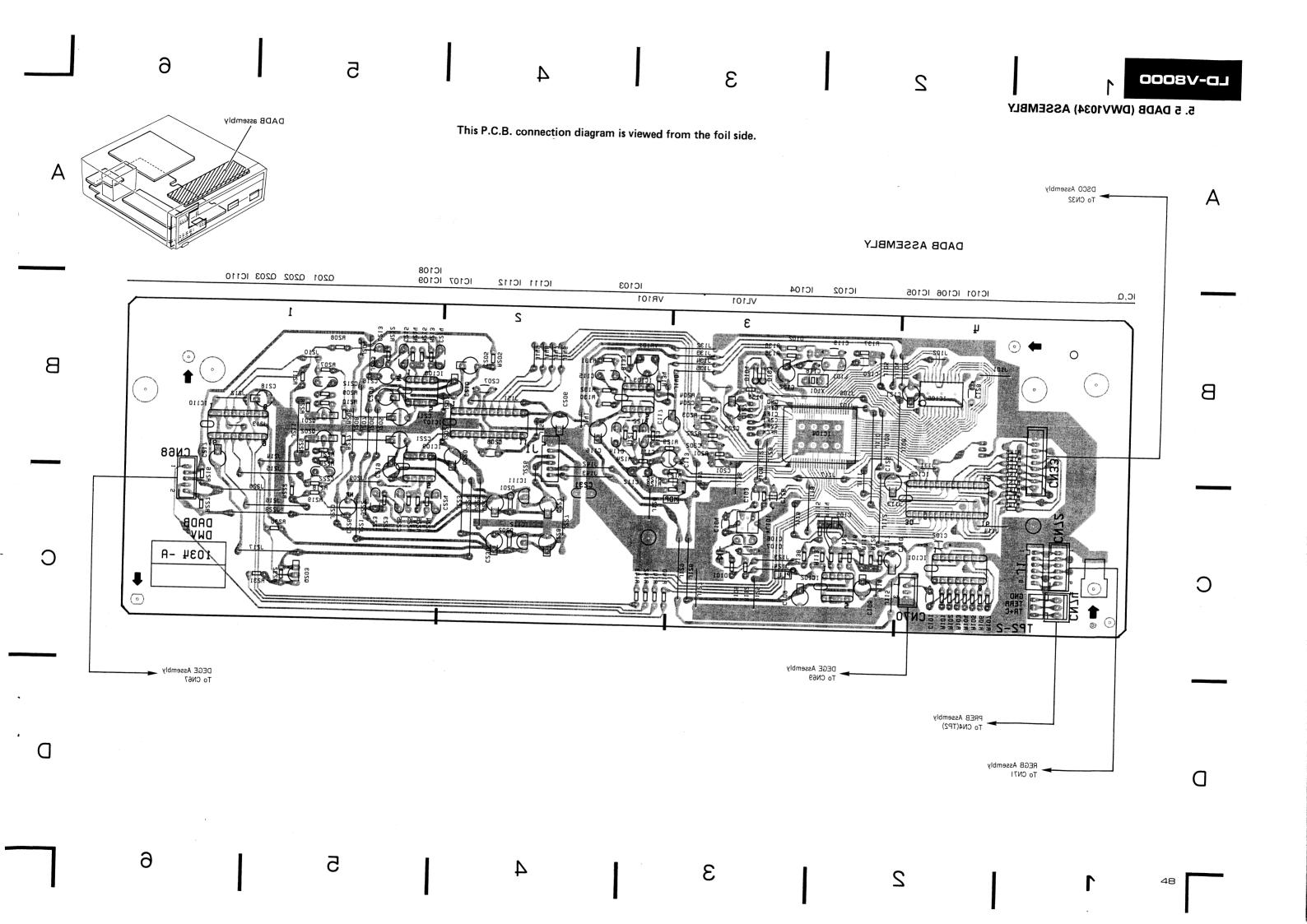

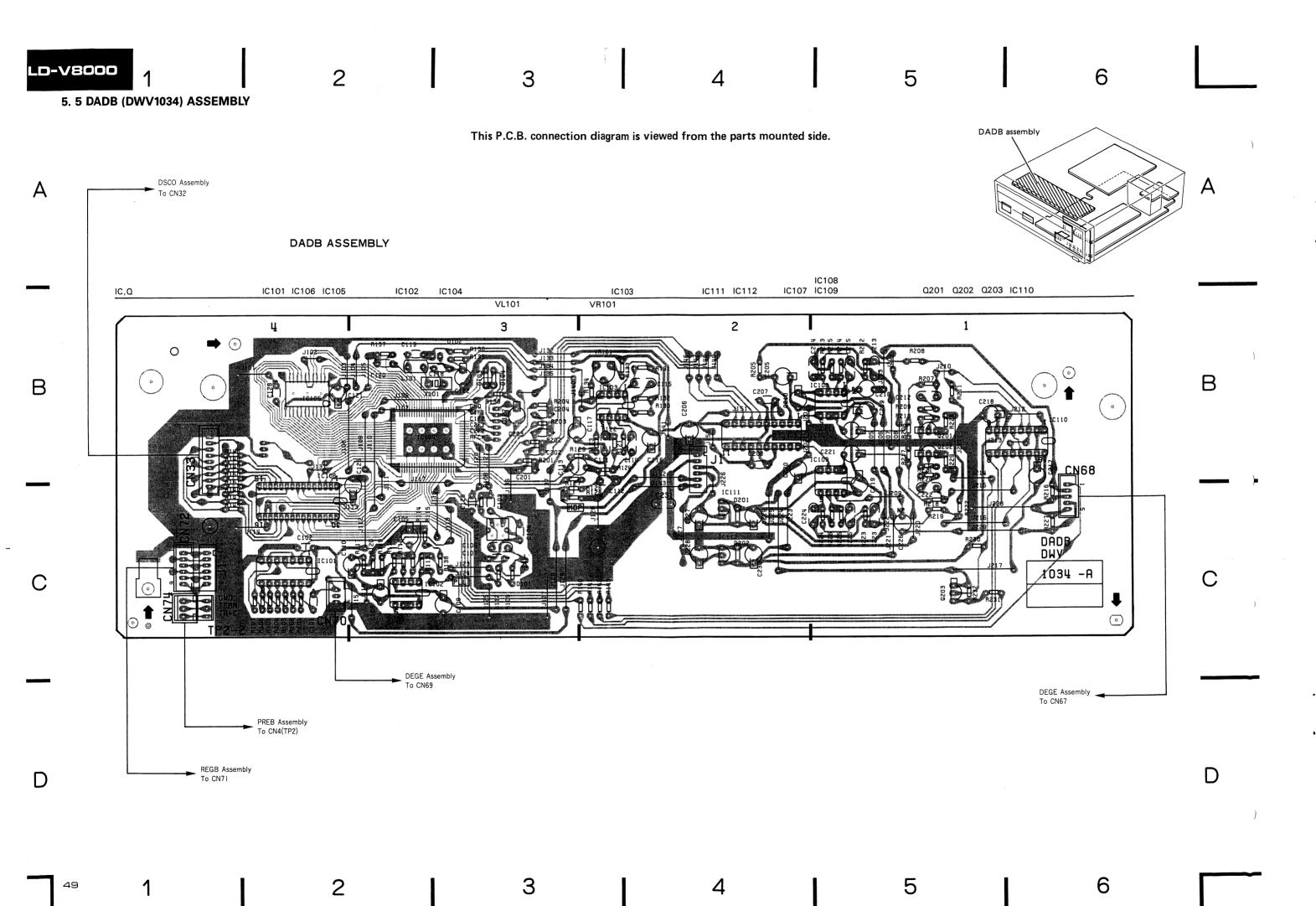

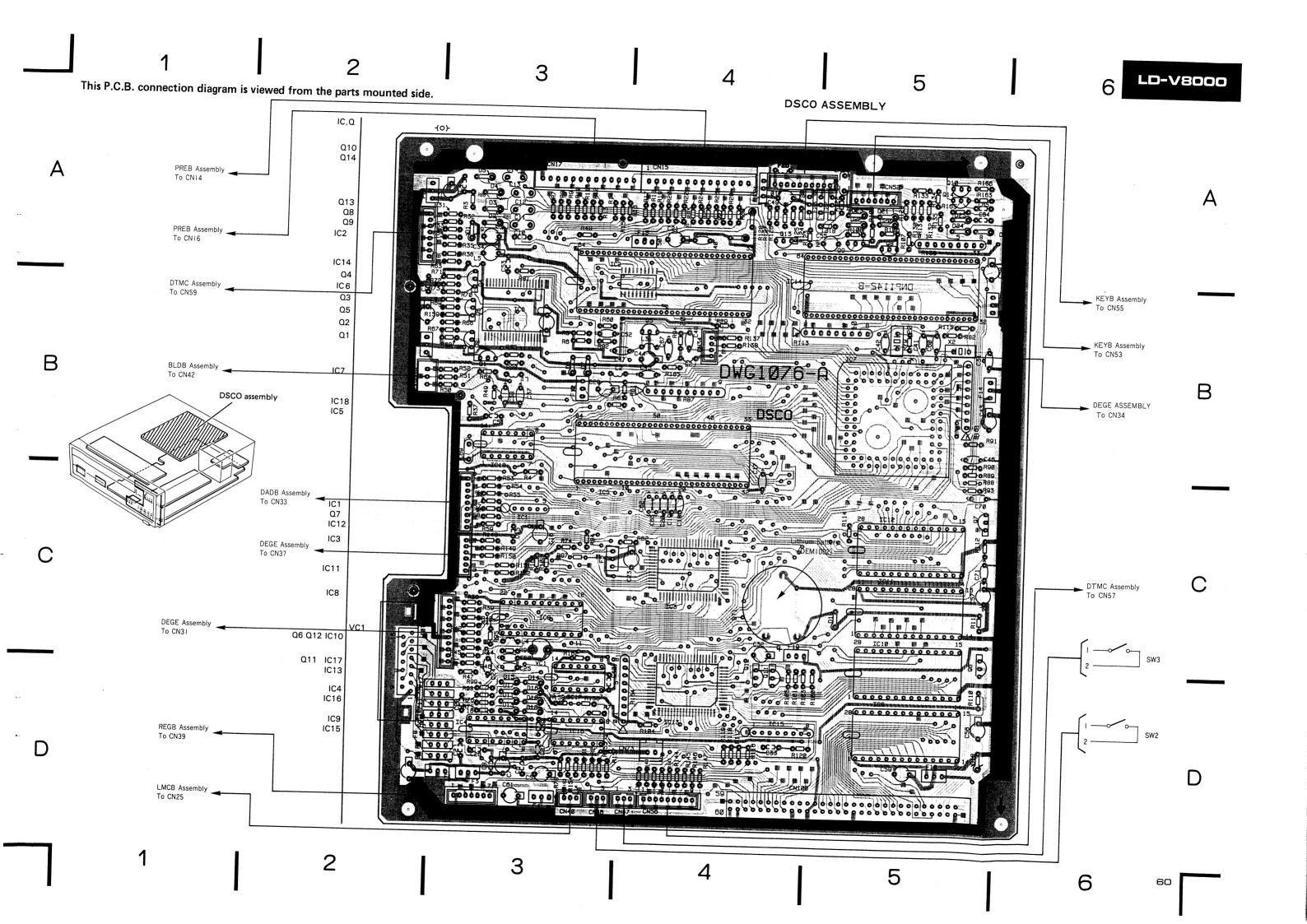

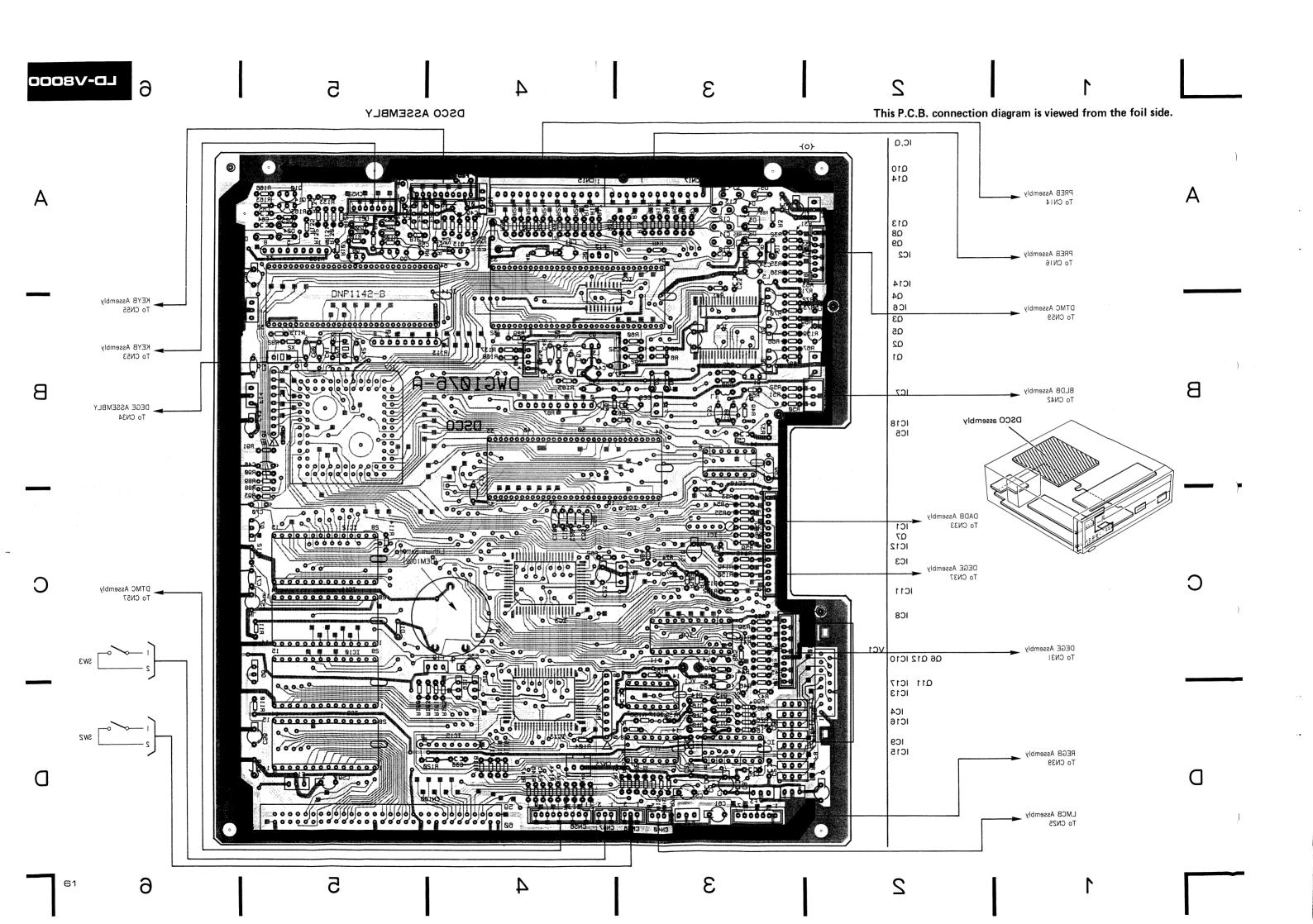

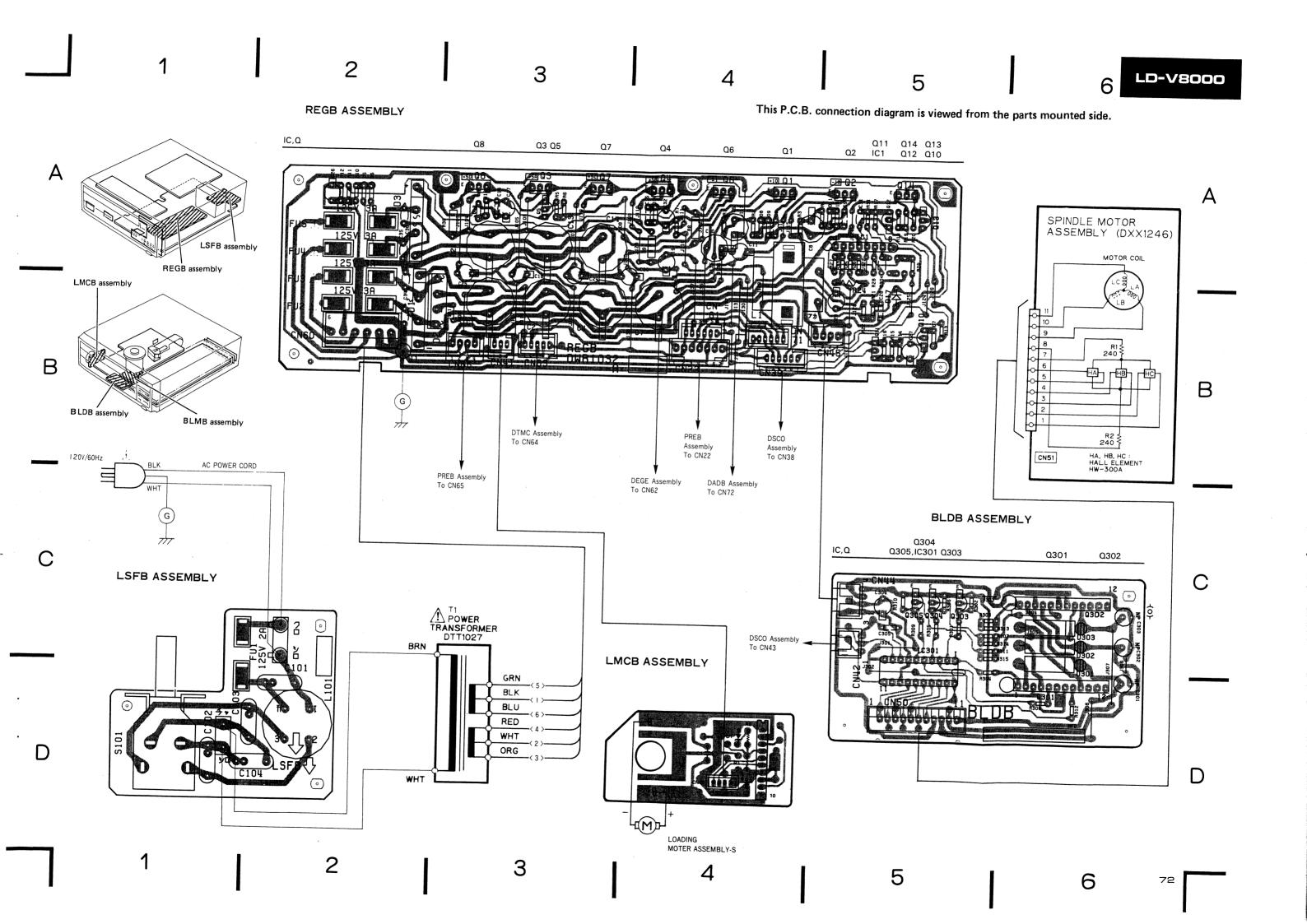

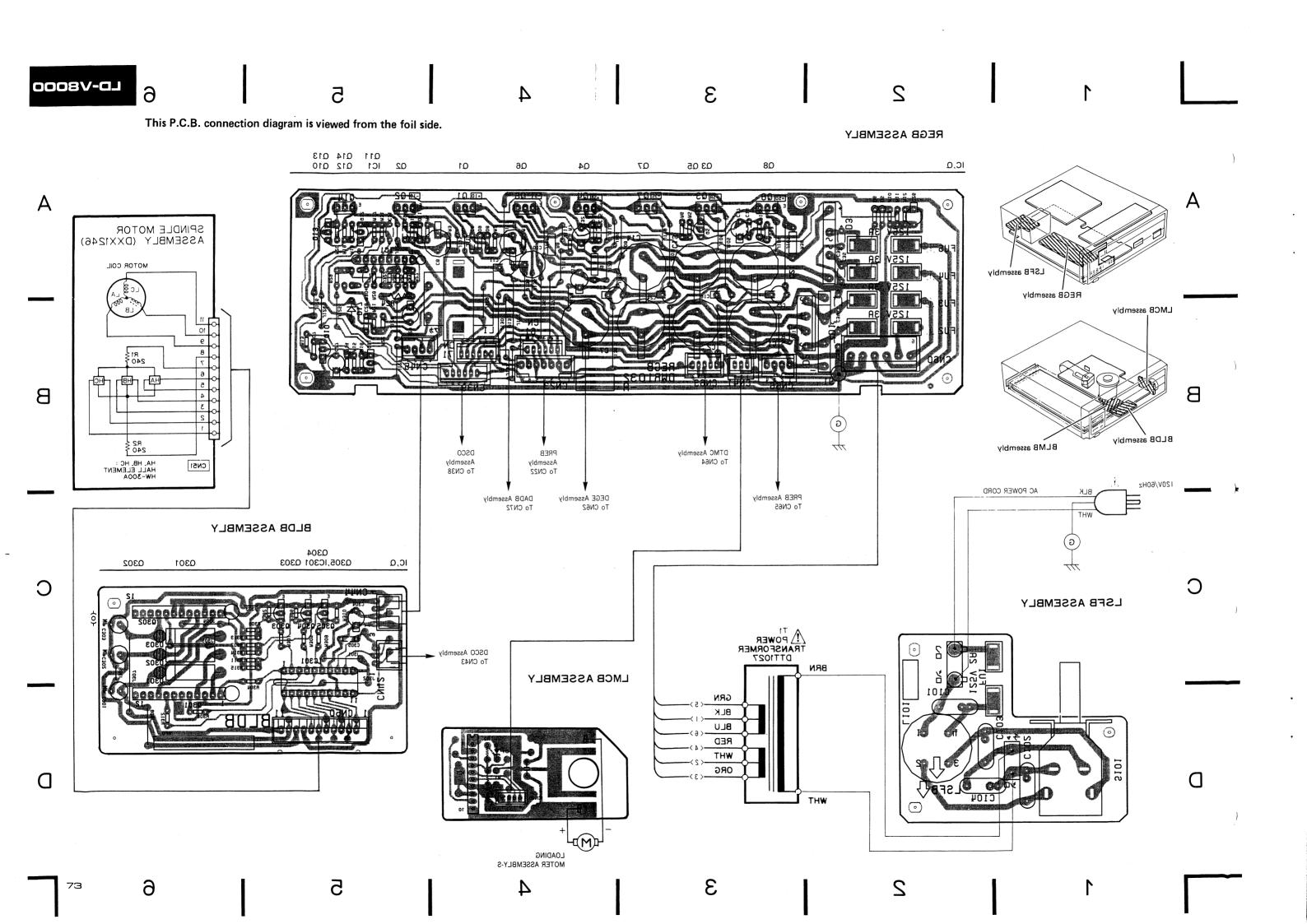

- This P.C.B. connection diagram is viewed from the parts mounted side.

The parts which have been mounted on the board can be replaced with those shown with the corresponding wiring symbols listed in the above Table.

The capacitor terminal marked with shows negative terminal.

The diode marked with shows cathode side.

- 5. The transistor terminal marked with \( \square\) shows emitter.

15

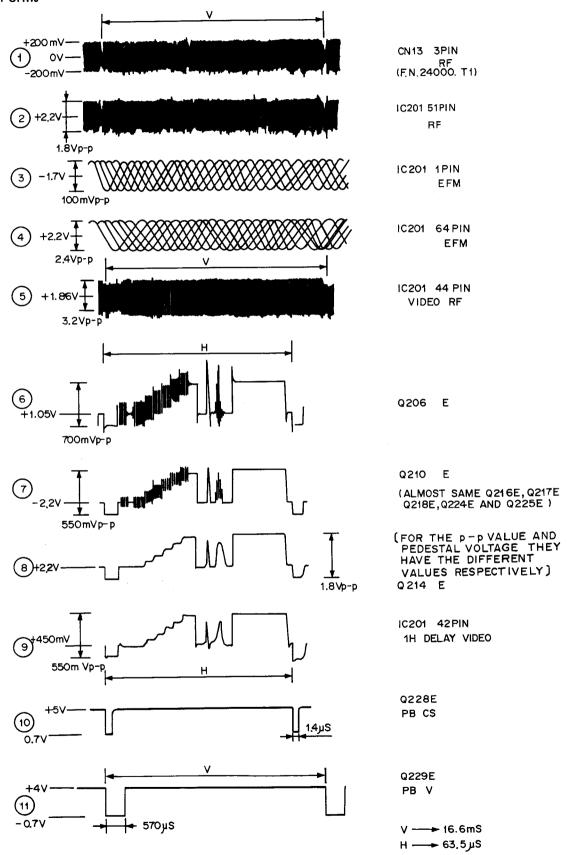

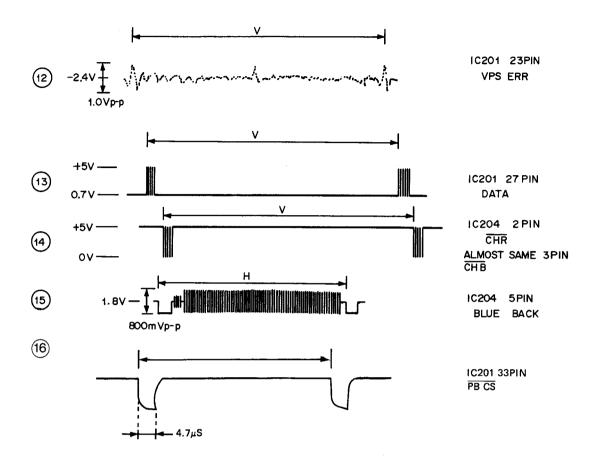

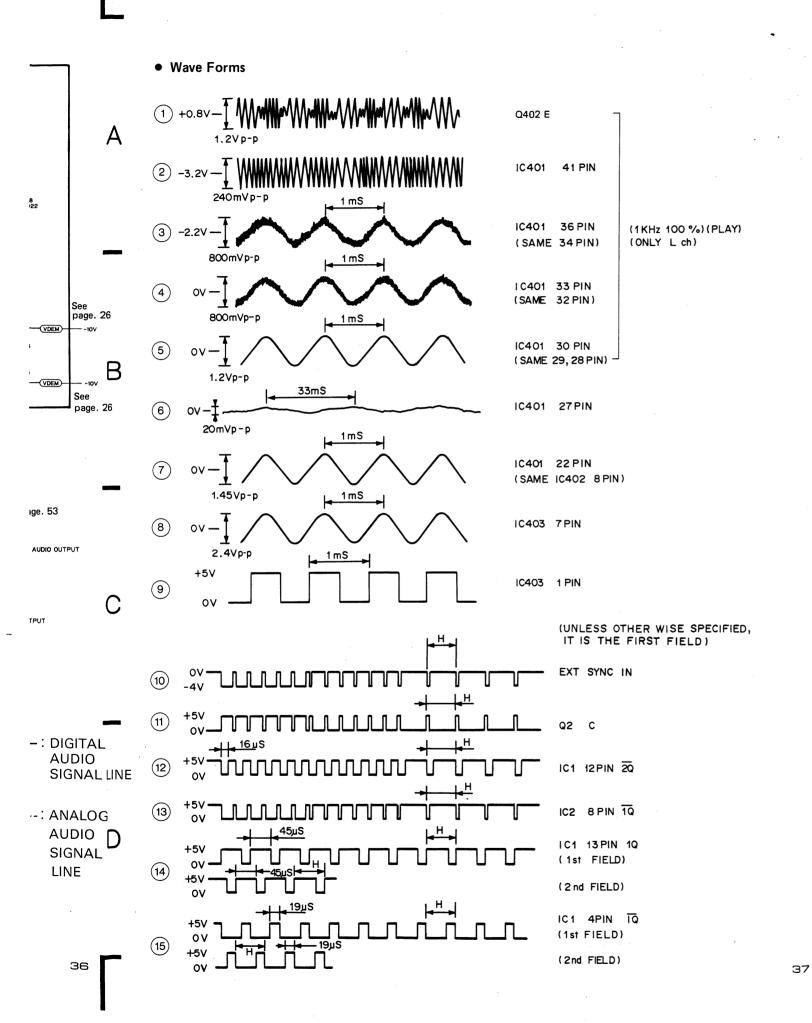

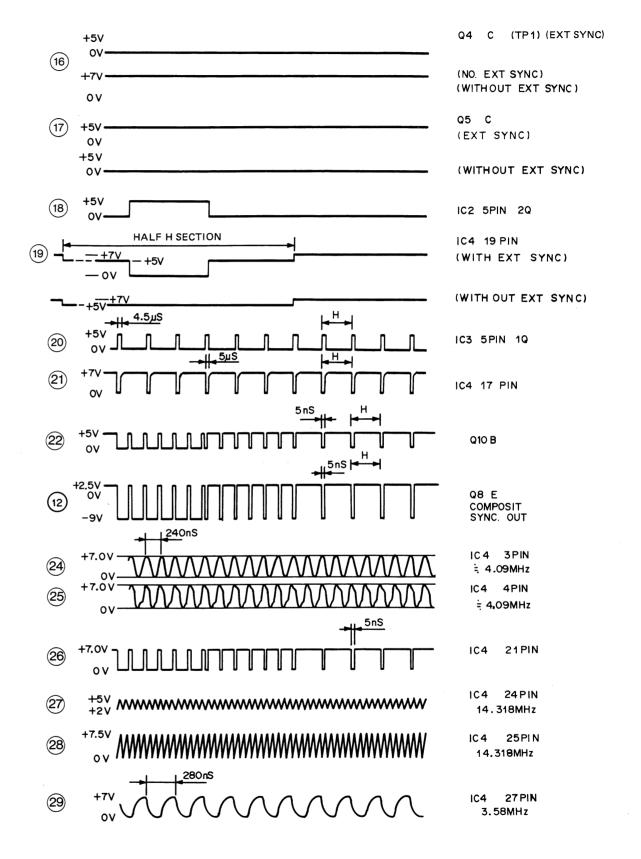

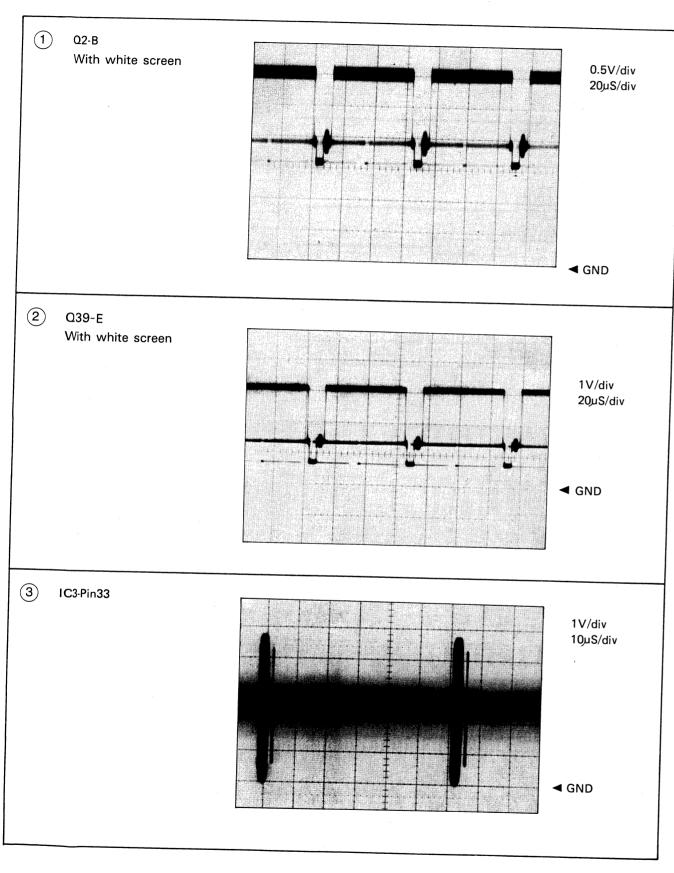

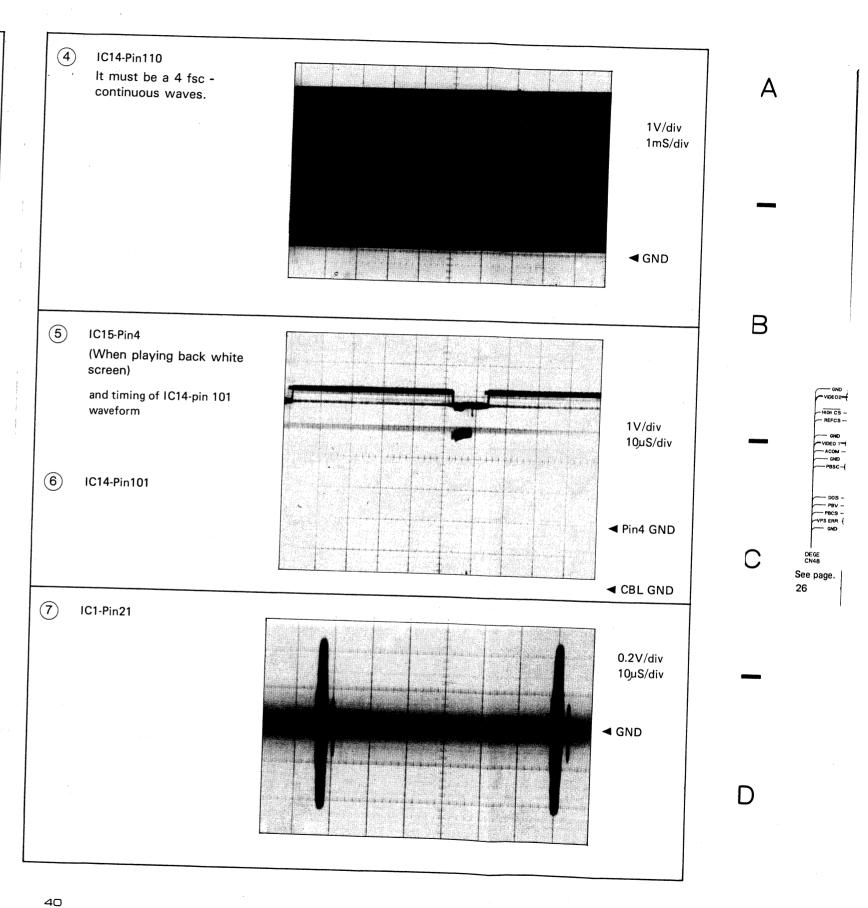

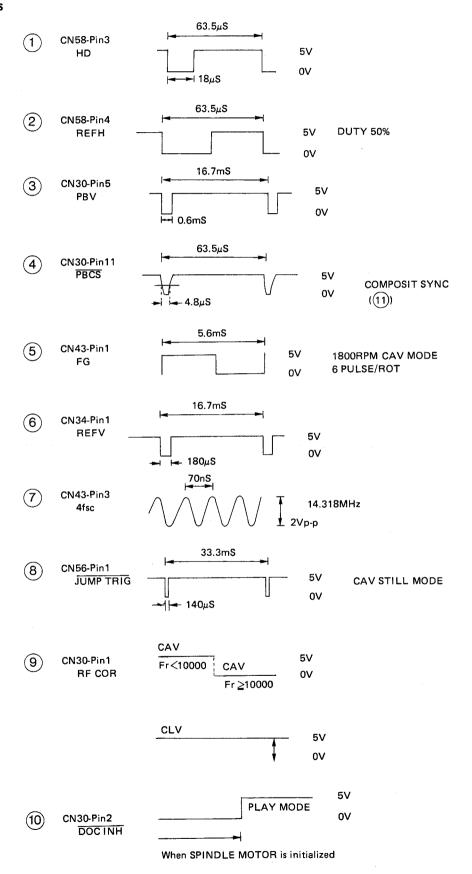

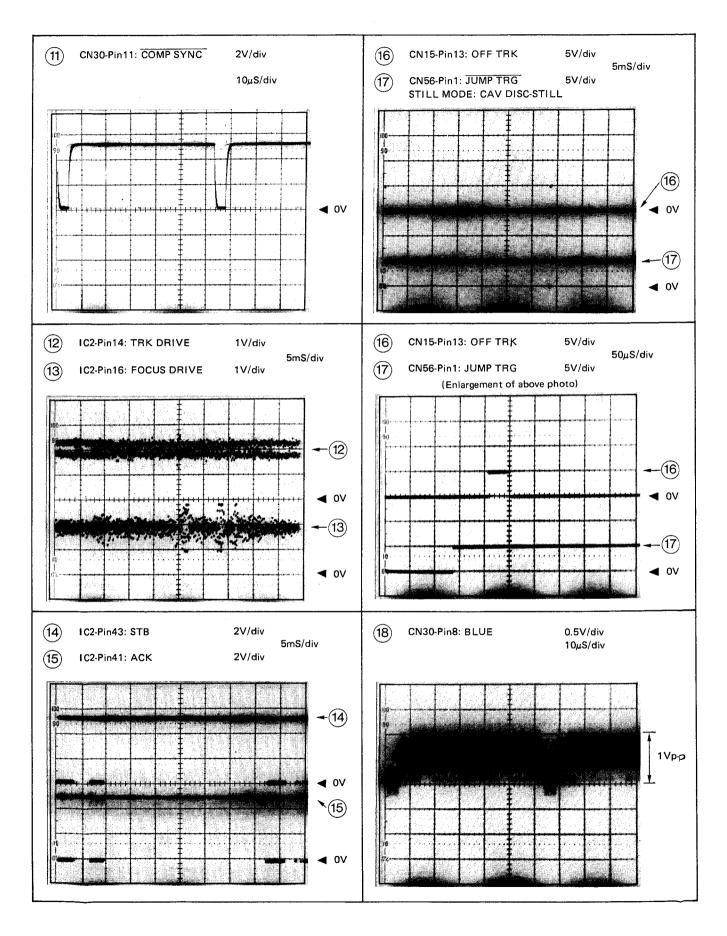

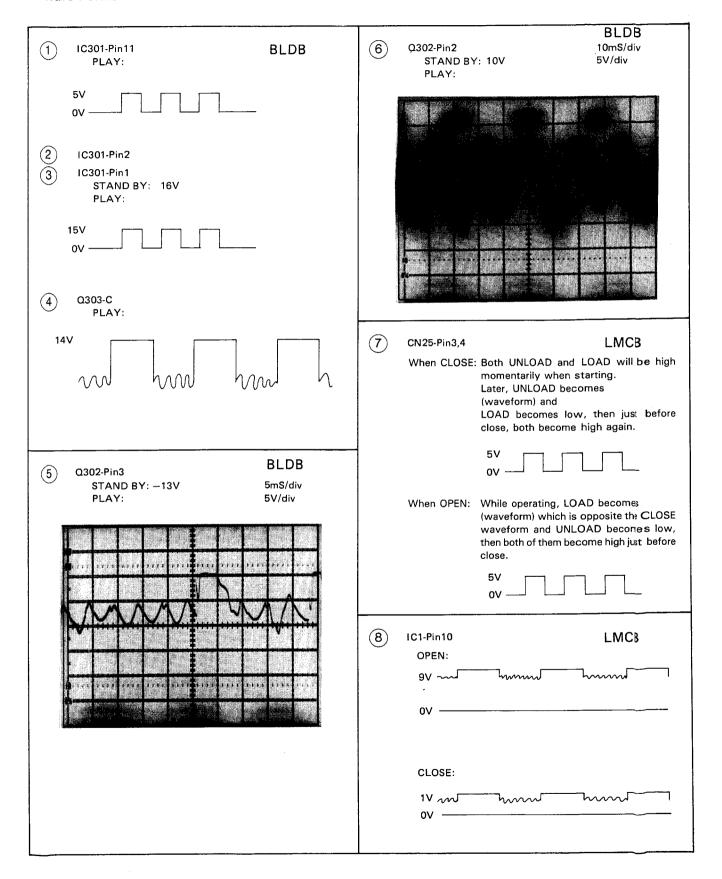

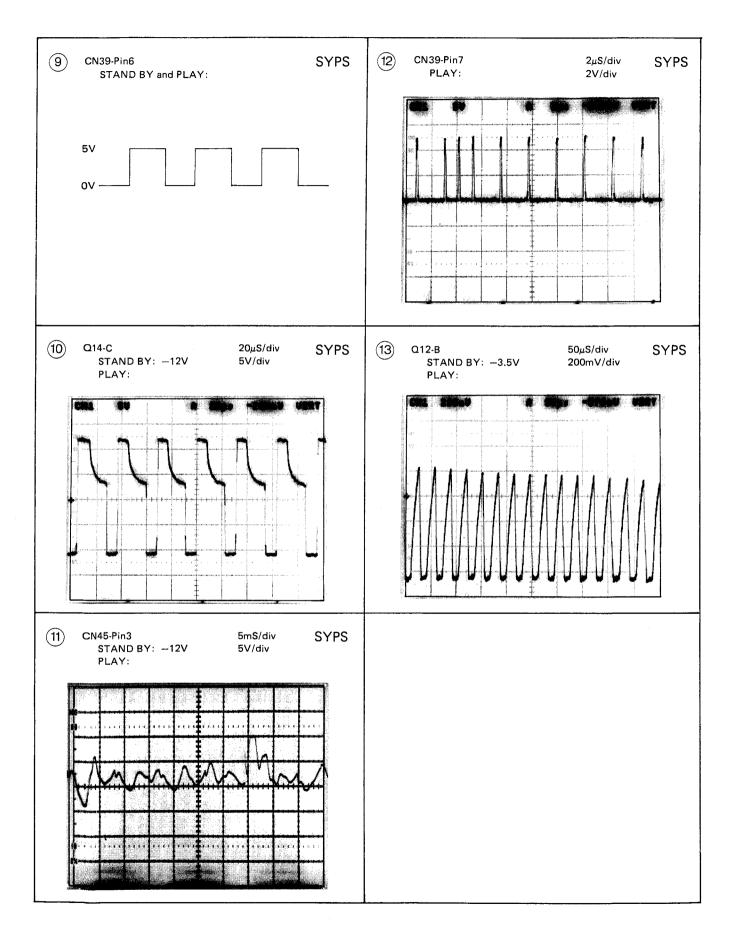

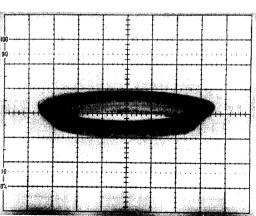

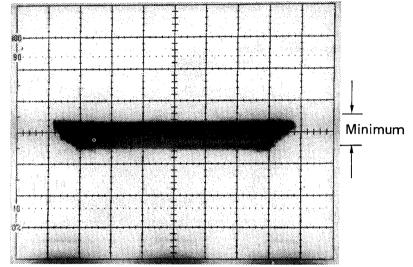

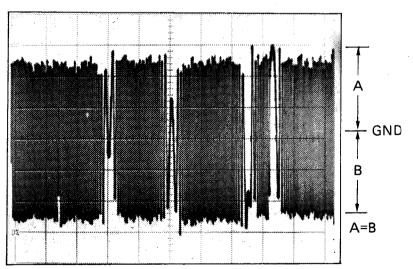

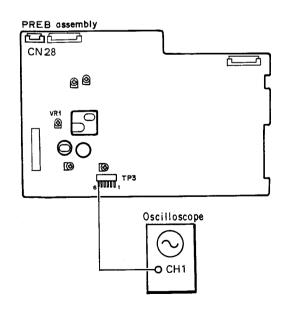

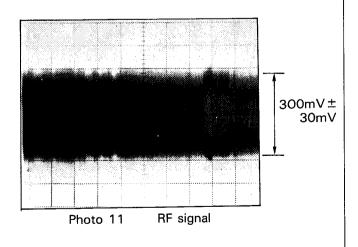

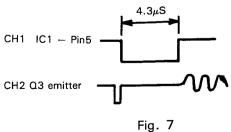

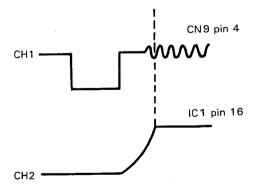

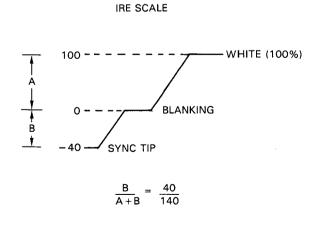

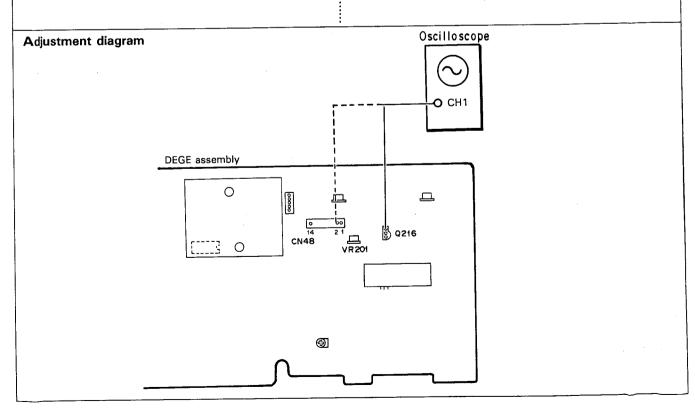

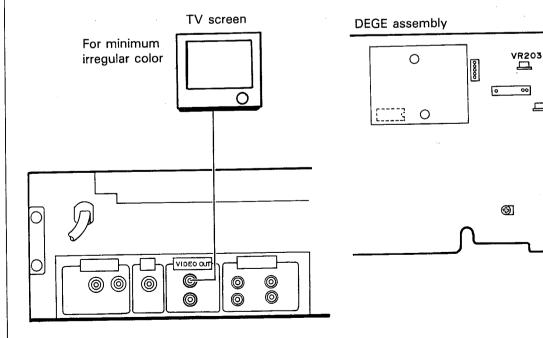

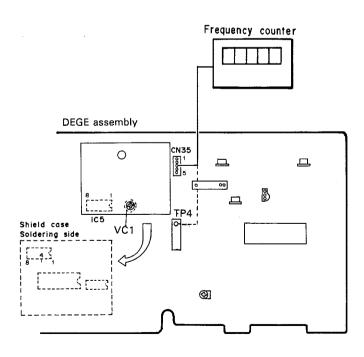

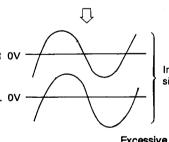

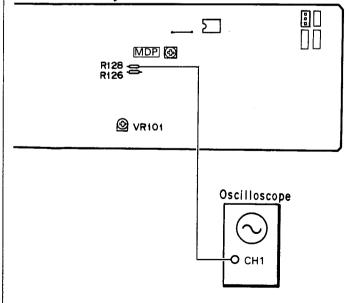

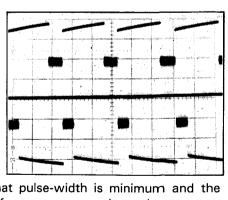

#### Wave Forms

38

# Wave Forms

### • Wave Forms

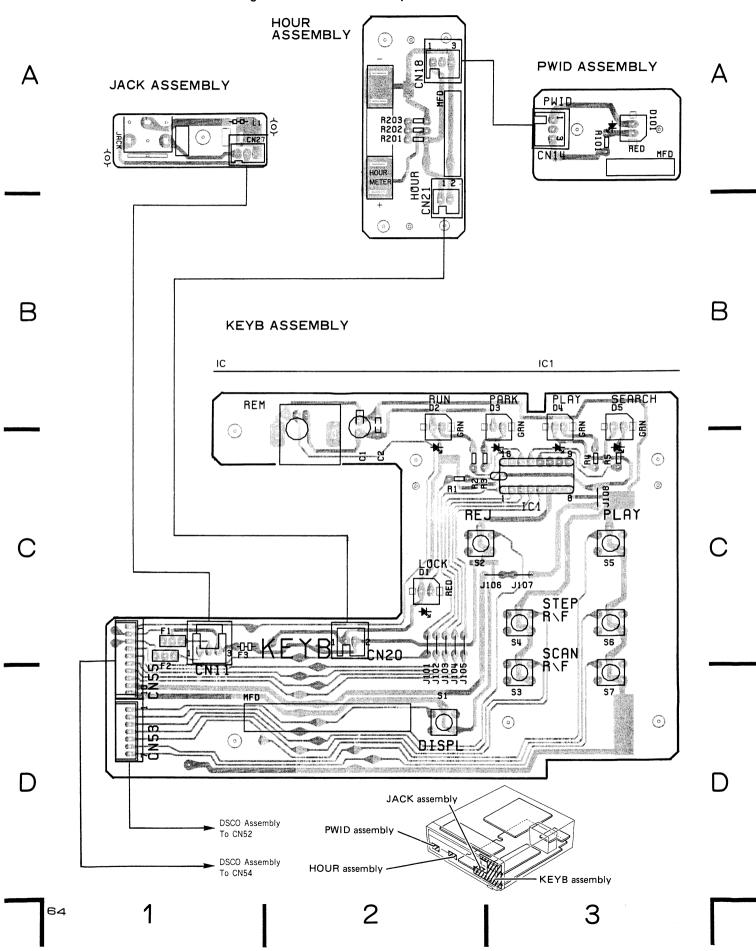

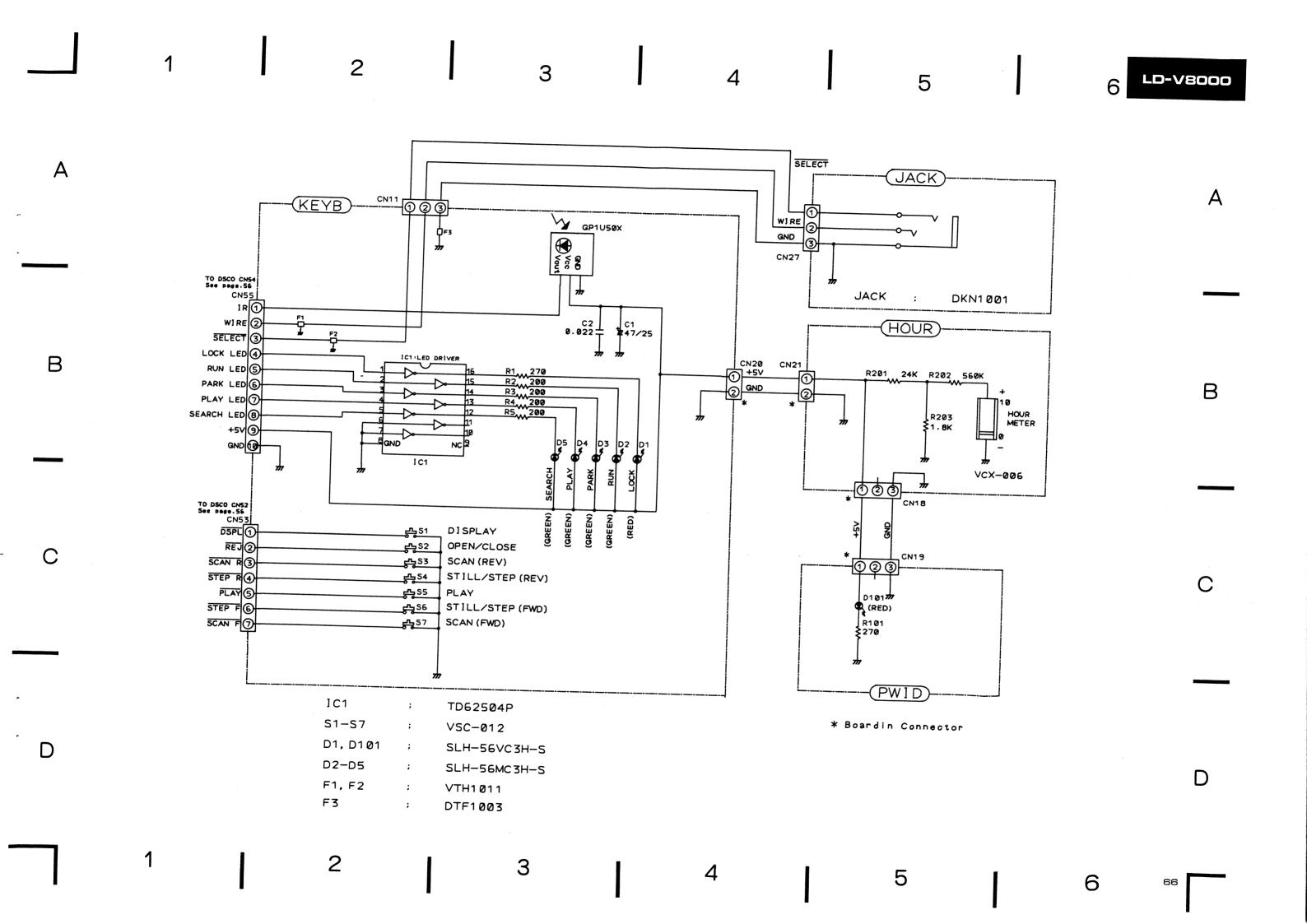

3 This P.C.B. connection diagram is viewed from the foil side. HOUR ASSEMBLY **PWID ASSEMBLY** Α JACK ASSEMBLY PWID RED В В KEYB ASSEMBLY IC IC1 REM 0 0 701L 901L STEP R\F SCAN R∖F MFD 0 JACK assembly DSCO Assembly To CN52 PWID assembly DSCO Assembly HOUR assembly To CN54 KEYB assembly 3

## 5.7 KEYB, HOUR, PWID AND JACK ASSEMBLIES

This P.C.B. connection diagram is viewed from the parts mounted side.

#### Wave Forms

## **6. ELECTRICAL PARTS LIST**

#### NOTES:

- Parts without part number cannot be supplied.

- Parts marked by "®" are not always kept in stock. Their delivery time may be longer than usual or they may be unavailable.

- The A mark found on some component parts indicates the importance of the safety factor of the part. Therefore, when replacing, be sure to use parts of identical designation.

- When ordering resistors, first convert resistance values into code form as shown in the following examples.

- Ex. 1 When there are 2 effective digits (any digit apart from 0), such as 560 ohm and 47k ohm (tolerance is shown by J = 5%, and K = 10%).

| $560\Omega$ | $56 \times 10^{1}$ | 561                                     | RD1/4PS 🗓 🛈 🗓 J            |

|-------------|--------------------|-----------------------------------------|----------------------------|

| $47k\Omega$ | $47 \times 10^{3}$ | 473                                     | RD1/4PS 🗗 🗇 🛈              |

| $0.5\Omega$ | 0R5                | • • • • • • • • • • • • • • • • • • • • | RN2H @ R 5 K               |

| $I\Omega$   | 010                | • • • • • • • • • • • • • • • • • • • • | <i>RS1P</i> 🛛 🗓 🛈 <i>K</i> |

Ex. 2 When there are 3 effective digits (such as in high precision metal film resistors).  $5.62k\Omega$   $562 \times 10^1$  5621.....RN1/4SR [5] [6] [2] [1] F

# Miscellaneous Parts P.C. BOARD ASSEMBLIES

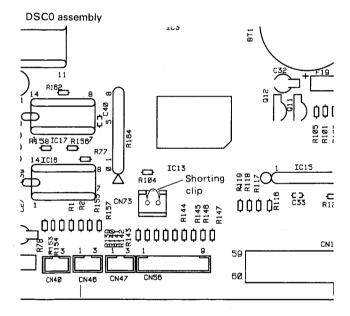

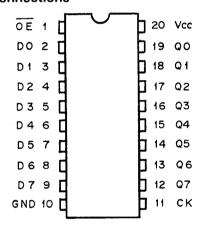

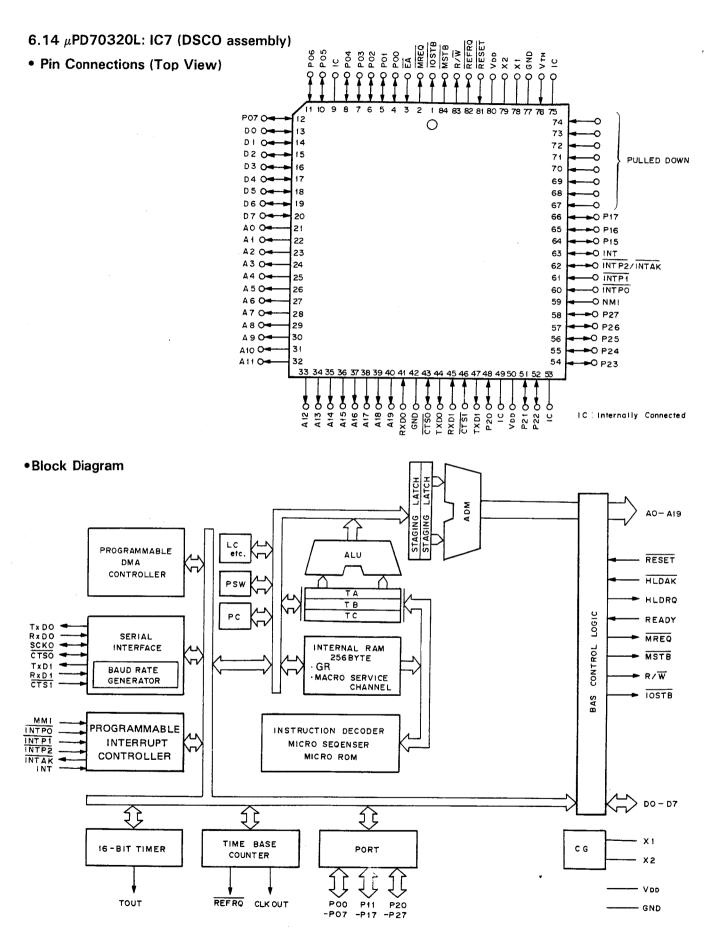

# DSCO Assembly (DWG1076) SEMICONDUCTORS

| Mark     | Symbol & D | escription              | Part No. | Mark | Symbol & Description | Part No.             |

|----------|------------|-------------------------|----------|------|----------------------|----------------------|

|          | DSCO asser | mbly                    | DWG1076  |      | IC3, IC13            | CXD1095Q             |

|          | JACK assen | •                       |          |      | IC12                 | HM6264P-12           |

|          | KEYB assem | nbly                    |          |      | IC6                  | MB90061-101          |

|          | HOUR asser | mbly                    |          |      | IC4                  | MC1454O6P            |

|          | PWID assem | •                       |          |      | IC1                  | M51953BL             |

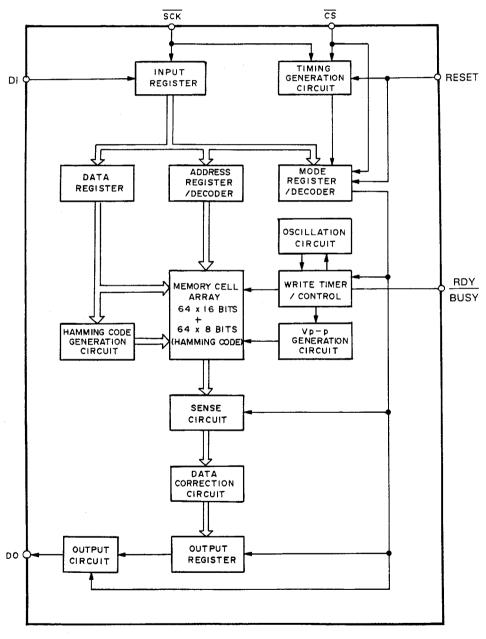

|          | REGB assem | nbly                    | DWR1032  |      | IC15                 | M6M80011L            |

|          | LSFB assem | bly                     |          |      | IC8                  | PD0011A              |

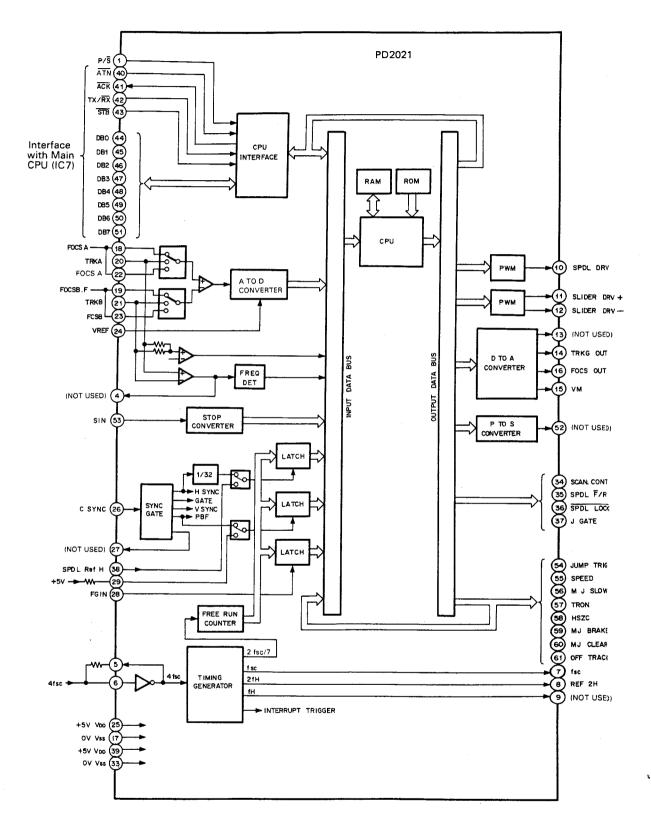

|          | DEGE assem | nbly                    | DWV1033  |      | IC2                  | PD2021               |

|          | DADB asser | nbly                    | DWV1034  |      | IC5                  | PD4183               |

|          | DTMC asser | mbly                    | DWV1035  |      | IC14                 | PD5109               |

|          | BLDB assem | ibly                    | DWR1031  |      | IC11                 | TC5564APL-15         |

|          | PREB assem | ibly                    | DWV1032  |      | IC16                 | TC74HCT04AP          |

|          | POSS assem | nbly                    |          |      | IC17                 | TC74HCO0AP           |

|          | HEAD assen | •                       |          |      | IC18                 | TC74HC1 4AP          |

|          | LMCB assen | nbly                    |          |      | IC7                  | μPD7032 <b>O</b> L-8 |

|          |            |                         |          |      | IC19                 | TC74HC574AF          |

|          |            | apacitors assembly      | DXX1248  |      |                      |                      |

|          |            | bly is incorporated in  |          |      | Q8, Q9, Q13          | UN4112               |

|          | DTMC asser | nbiy.)                  |          |      | Q11, Q12             | UN4212               |

|          |            |                         |          |      | Ω3, Ω10              | 2SA933 <b>S</b>      |

| OTHER    | RS         |                         |          |      | Q1, Q2, Q4, Q7       | 2SC174OS             |

| Mark     | Symbol & D | escription              | Part No. |      | Q6                   | 2SD1859              |

| Δ        |            | AC power cord           | DDG1001  |      | Q5                   | 2SK 16               |

| $\Delta$ | T1         | Power transformer       | DTT1027  |      | Q14                  | 2SK184               |

|          | IC9        | Program EPROM           | DYW1041  |      |                      |                      |

|          | IC10       | Program EPROM           | DYW1042  |      | D1                   | MTZ3.IB              |

|          |            | Hour meter              | VCX-006  |      | D2 - D5              | MTZ5.1B              |

|          |            |                         |          |      | D18                  | MTZ5.6C              |

|          |            | Strain relief           | VEC-201  |      | D6 - D17,D19 - D26   | 1SS25₄               |

| $\Delta$ | FU2 - FU5  |                         | VEK-018  |      |                      |                      |

| $\Delta$ | FU1        | Fuse (2A)               | VEK-021  |      |                      |                      |

|          |            | Pick-up assembly        | DWY1007  |      |                      |                      |

|          |            | Plunger                 | DXP1001  |      |                      |                      |

|          | Spir       | ndle motor assembly-S   | DXX1246  |      |                      |                      |

|          |            | Tilt motor assembly-S   | DXX1219  |      |                      |                      |

|          | M1 Loa     | ding motor assembly-S   | VXX1084  |      |                      |                      |

|          | S2         | Slide switch (TABLE/IN) | VSK-010  |      |                      |                      |

|          | S3 S       | lide switch (TABLE/OUT) | VSK-012  |      |                      |                      |

# LD-V8000

### **COILS AND FILTERS**

| Mark | Symbol & De                   | scription                               | Part No. |

|------|-------------------------------|-----------------------------------------|----------|

|      | L1                            | Axial inductor                          | LAU100J  |

|      | L2                            | Axial inductor                          | LAU101J  |

|      | L3                            | Axial inductor                          | LAU3R3K  |

|      | L4                            | Axial inductor                          | LAU221J  |

|      | L5                            | Radial inductor                         | LRA101K  |

|      | F1 — F5, F1:                  | 2 — F15, F18 — F21<br>3 terminal filter | VTH1001  |

|      | F6 — F11, F16, F17, F22 — F24 |                                         | VTH1011  |

|      | F25, F26                      | Ferrite bead                            | DTF1003  |

### **CAPACITORS**

| Mark | Symbol & Des  | scription                                            | Part No.     |

|------|---------------|------------------------------------------------------|--------------|

|      | C31, C60      |                                                      | CCCCH150J50  |

|      | C37 C38, C50  | 0                                                    | CCCCH220J50  |

|      | C41 C42       |                                                      | CCCCH270J50  |

|      | C17, C22, C24 | 4, C25, C62, C63                                     | CCCSL101J50  |

|      | C67           |                                                      | CCCCH180J50  |

|      | C18 — C20     |                                                      | CCCSL330J50  |

|      | C57           |                                                      | CEANL470M10  |

|      | C55           |                                                      | CEANP100M16  |

|      | C16           |                                                      | CEASR47M50   |

|      | C1, C7, C56   |                                                      | CEAS100M50   |

|      | ,,            | 221, C23, C29, C32,<br>3, C44, C49, C58,             | CEAS470M10   |

|      | C68           |                                                      | CEAS331M6R3  |

|      | C45, C52      |                                                      | CKCYF103Z50  |

|      | C70, C71, C4  | 6, C53, C65                                          | CKPUYB101K50 |

|      |               | 08, C10, C15,<br>C33, C35, C39, C40,<br>i1, C64, C66 | CKPUYF223Z25 |

|      | C54           |                                                      | CQMA104J50   |

|      | C11 - C14     |                                                      | CQMA393J50   |

|      | C69           |                                                      | CQMA473J50   |

|      | VC1           | Ceramic trimmer (70nF)                               | VCM-009      |

### **RESISTORS**

| Mark | Symbol & Description                                                                | Part No.    |

|------|-------------------------------------------------------------------------------------|-------------|

|      | R113, R136, R161, R164                                                              | RA8S103J    |

|      | Resistor array $(10k\Omega \times 8)$<br>R87 Resistor array $(2.2k\Omega \times 8)$ | RA9S222J    |

|      | Other resistors                                                                     | RD1/6PM□□□J |

### **OTHERS**

| Mark | Symbol | & Description     | Part No. |

|------|--------|-------------------|----------|

|      | BT1    | Lithium battery   | DEM1002  |

|      |        | 84 pin IC socket  | DKH1001  |

|      | X2     | Crystal resonator | DS\$1001 |

|      | X1     | Crystal resonator | DSS1010  |

|      |        | IC socket         | VKH-029  |

|      |        | 28 pin IC socket  | VKH1001  |

|      |        | D-SUB connector   | DXX1031  |

|      |        | assembly (15 pin) |          |

# JACK Assembly OTHER

| Mark | Symbol & Description | Part No. |

|------|----------------------|----------|

|      | Stereo mini jack     | DKN1001  |

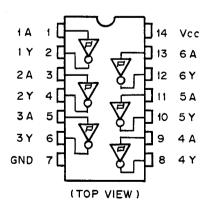

# KEYB Assembly SEMICONDUCTORS

| Mark | Symbol & | Description      | Part No.   |  |

|------|----------|------------------|------------|--|

|      | IC1      | Transistor array | TD62504P   |  |

|      | D2 - D5  |                  | SLH-56MC3H |  |

|      | D1       |                  | SLH-56VC3H |  |

## **SWITCHES**

| Mark | Symbol & I | Description          | Part No. |  |

|------|------------|----------------------|----------|--|

|      | S1 - S7    | Tact switch          | VSC-012  |  |

|      |            | (PLAY, REJECT,       |          |  |

|      |            | STEP.R, STEP F, SCAN |          |  |

|      |            | R, SCAN F, DISPLAY)  |          |  |

#### **FILTERS**

| Mark | Symbol & Description |              | Part No. |

|------|----------------------|--------------|----------|

|      | F3                   | Ferrite bead | ATF1003  |

|      | F1, F2               | EMI filter   | VTH1011  |

#### CAPACITORS

| Mark | Symbol & Description | CFAS470M25   |  |

|------|----------------------|--------------|--|

|      | C1                   | CEAS470M25   |  |

|      | C2                   | CKPUYF223Z25 |  |

### RESISTORS

| Mark | Symbol & Description | Part No.    |  |

|------|----------------------|-------------|--|

|      | All resistors        | RD1/6PM□□□J |  |

|      |                      |             |  |

### OTHER

| Mark | Symbol & Description | Part No. |

|------|----------------------|----------|

|      | IR sensor unit       | GP1U50X  |

| PWID   | Assembly                |                                         | Mark         | Symbol & Description                                         | Part No.                           |

|--------|-------------------------|-----------------------------------------|--------------|--------------------------------------------------------------|------------------------------------|

|        |                         |                                         |              | C30                                                          | CKCYB332K50                        |

| SEIVII | CONDUCTORS              |                                         |              | C33 - C36                                                    | CKCYF103Z50                        |

| Mark   | Symbol & Description    | Part No.                                |              | C28                                                          | CKPUYB471K50                       |

|        | D101                    | SLH-56VC3H                              |              | C6, C9, C15, C16<br>C31                                      | CKPUYF223Z25<br>CQMA102K50         |

| RESIS  | TOR                     |                                         | DEGIC        | TORS                                                         |                                    |

| Mark   | Symbol & Description    | Part No.                                |              |                                                              | David No.                          |

|        | R101                    | RD1/6PM271J                             | Mark         | Symbol & Description                                         | Part No.                           |

| HOUR   | R Assembly              | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |              | R24 (3W 0.47Ω)<br>R8, R9, R30<br>R23, R25 — R27              | DCN1013 RD1//2PMF□□□J RN1/6PQ□□□□F |

|        | TORS                    |                                         |              | R22 (1W 2.7Ω)                                                | VCN-100                            |

| Mark   | Symbol & Description    | Part No.                                |              | Other resistors                                              | RD1/6PM□□□J                        |

|        | All resistors           | RD1/6PM□□□J                             |              |                                                              |                                    |

|        |                         |                                         | LSFB<br>SWIT | Assembly<br>CH                                               |                                    |

| REGB   | Assembly (DWR1032)      |                                         | Mark         | Symbol & Description                                         | Part No.                           |

| SEMIC  | CONDUCTORS              |                                         | Δ            | S101 Power switch                                            | VSA-011                            |

| Mark   | Symbol & Description    | Part No.                                | 24           | S TO TOWN SWILLIAM                                           |                                    |

|        | IC1                     | <br>M5218L                              | FU TE        | n                                                            |                                    |

|        | IC 1                    | WISZTOL                                 | FILTE        |                                                              |                                    |

|        | Q10, Q12                | 2SA933S                                 | Mark         | Symbol & Description                                         | Part No.                           |

|        | Q2, Q6                  | 2SB941                                  | Δ            | L101 Line filter                                             | VTL-157                            |

|        | Q13<br>Q11              | 2SC1627<br>2SC1740S                     |              |                                                              |                                    |

|        | Q5                      | 2SC3243                                 | CAPA         | CITORS                                                       |                                    |

|        | Q1, Q3, Q4, Q7, Q8, Q14 | 2SD1267                                 | Mark         | Symbol & Description                                         | Part No.                           |

|        | D9, D10                 | HZS10NB2                                |              |                                                              | RCG-009                            |

|        | D13, D14                | HZS5.6NB2                               | Δ            | C101 — C104 Ceramic capacitor (0.01 µF/AC400V)               | NCG-009                            |

|        | D2                      | RB-152LF-F                              |              | (2.2.)                                                       |                                    |

|        | D1<br>D3                | RBA-402<br>RBV-402                      | DECE         | A                                                            |                                    |

|        | D3                      | NBV-402                                 |              | Assembly (DWV1033)                                           |                                    |

|        | D17                     | S2K20                                   | SEMIC        | CONDUCTORS                                                   |                                    |

|        | D5 — D8, D11, D12       | 1SS254                                  | Mark         | Symbol & Description                                         | Part No.                           |

|        |                         |                                         |              | IC4                                                          | HD440072                           |

| COIL   |                         |                                         |              | IC1, IC3                                                     | HD74H(2 21P                        |

| Mark   | Symbol & Description    | Part No.                                |              | IC2<br>IC403                                                 | HD74H(74P<br>M5233F                |

|        |                         | VTT-070                                 |              | IC402                                                        | NJM4588S                           |

|        | L1 Choke coil           | V11-070                                 |              |                                                              |                                    |

|        |                         |                                         |              | IC5                                                          | NJU4053BD<br>PA0034A               |

| CAPA   | CITORS                  |                                         |              | IC401<br>IC202                                               | PA3018                             |

| Mark   | Symbol & Description    | Part No.                                |              | IC201                                                        | PA5010                             |

|        | C27, C29                | CEAS100M50                              |              | IC204                                                        | PA9003                             |

|        | C18 — C20, C24, C25     | CEAS101M10                              |              | 10203                                                        | PM0001                             |

|        | C13, C21                | CEAS103M10                              |              | IC203<br>IC6                                                 | TC405(3)P                          |

|        | C5, C8, C10             | CEAS221M25                              |              | .50                                                          |                                    |

|        | C26                     | CEAS4R7M50                              |              | Q3, Q4, Q404, Q412                                           | UN4212                             |

|        | C11                     | CEAS470M25                              |              | Q1, Q5, Q8 — Q10, Q201, Q202,                                | 2SA933S                            |

|        | C1, C2, C4, C7          | CEAS472M25                              |              | Q219, Q220, Q226, Q228, Q405,                                |                                    |

|        | C14                     | CEAS682M10                              |              | Q411, Q413                                                   | 2SC1740 <b>S</b>                   |

|        | C32                     | CEHAQ331M6R3                            |              | Q2, Q6, Q203 — Q218, Q224,<br>Q225, Q227, Q229 — Q331, Q401, |                                    |

|        | C17                     | CEHAQ470M10                             |              | Q402, Q406 — Q410                                            |                                    |

## LD-V8000

| Mark  | Symbol & De                | escription                              | Part No.                   | Mark | Symbol & Description              | Part No.                   |

|-------|----------------------------|-----------------------------------------|----------------------------|------|-----------------------------------|----------------------------|

|       | Q11                        |                                         | 2SC3581                    |      | C286, C288, C245                  | CCCCH470J50                |

|       | Q12                        |                                         | 2SK161                     |      | C306, C422, C423                  | CCCCH560J50                |

|       | Q403                       |                                         | 2SK184                     |      | C305                              | CCCCH620J50                |

|       | Q403                       |                                         | 23K 104                    |      | C33, C253                         | CCCCH680J50                |

|       | 50                         |                                         | 1170704                    |      |                                   | CCCCH820J50                |

|       | D6                         | D004 D404 D444                          | HZS7B1                     |      | C209, C210                        | CCCC11020330               |

|       |                            | D201, D401 — D411,                      | 1SS254                     |      | 2007                              | 0000001010150              |

|       | D414                       |                                         | 40) (00                    |      | C307                              | CCCCH910J50                |

|       | D3, D4, D7                 |                                         | 1SV68                      |      | C275                              | CCCSL121J50                |

|       |                            |                                         |                            |      | C19, C34, C295, C296              | CCCSL151J50                |

|       |                            |                                         |                            |      | C261, C262, C279                  | CCCSL181J50                |

| SWITC | CH AND RE                  | LAY                                     |                            |      | C290                              | CCCSL241J50                |

| Mark  | Symbol & De                | escription                              | Part No.                   |      | C24, C211, C419                   | CCCSL271J50                |

|       | S1                         | Lever switch                            | VSK-005                    |      | C418                              | CCCSL301J50                |

|       | RY401                      |                                         | VSR-005<br>VSR-005         |      | C246, C328                        | CCCSL331J50                |

|       | N1401                      | Relay                                   | V3N-003                    |      | C212                              | CCCSL391J50                |

|       |                            |                                         |                            |      |                                   | CCCSL681J50                |

| COLLE | AND FILTE                  | :De                                     |                            |      | C466                              | CCC3E001330                |

| CUILS | AND FILL                   | ino                                     |                            |      | C25                               | CCCUJ270J50                |

| Mark  | Symbol & De                | escription                              | Part No.                   |      |                                   | CEANLR47K50                |

|       | 1.005                      | A - A - E A - A - A - A - A - A - A - A |                            |      | C441                              |                            |

|       | L205                       | Axial inductor                          | LAU100J                    |      | C444                              | CEANP2R2M50<br>CEANP220M10 |

|       | L2, L202, L2               |                                         | LAU120J                    |      | C263, C424, C425, C430, C431      |                            |

|       |                            | Axial inductor                          | 1.4114641                  |      | C260                              | CEANP3R3M50                |

|       | L209                       | Axial inductor                          | LAU121J                    |      | 0074 0070 0440                    | OF A ND 4 7 0 144 0        |

|       | L204                       | Axial inductor                          | LAU150J                    |      | C271, C276, C442                  | CEANP470M10                |

|       |                            |                                         |                            |      | C229, C327                        | CEASR47M50                 |

|       | L206                       | Axial inductor                          | LAU220J                    |      | C201, C329, C443, C465            | CEAS010M50                 |

|       | L215                       | Axial inductor                          | LAU330J                    |      | C7, C30, C219, C299, C308, C440,  | CEAS100M50                 |

|       | L201, L218                 | Axial inductor                          | LAU390J                    |      | C449, C452, C453                  |                            |

|       | L220                       | Axial inductor                          | LAU470J                    |      | C320, C322, C332, C333,           | CEAS221M6R3                |

|       | L216                       | Axial inductor                          | LAU560J                    |      | C414 - C417, C436, C437           |                            |

|       | L219                       | Axial inductor                          | LAU680J                    |      | C13, C40, C43, C39, C408, C409    | CEAS331M16                 |

|       | L213                       | Axial inductor                          | LAU820J                    |      | C1, C2, C38, C42                  | CEAS331M6R3                |

|       |                            |                                         | LRA221J                    |      | C17, C222, C285, C439, C458,      | CEAS4R7M50                 |

|       | L213, L214,<br>L5          | L3, L4 Radial inductor                  | LRA222K                    |      | C459                              | CEACHITAGO                 |

|       |                            | Radial inductor                         |                            |      | C3, C11, C12, C16, C29, C31, C41, | CEAS470M16                 |

|       | L207, L208                 | Radial inductor                         | LRA391K                    |      | C206, C208, C224, C226, C228,     | CLASTICITIO                |

|       | 1011                       | Dadial industra                         | I DA EG1V                  |      | C231, C236, C249, C252, C255,     |                            |

|       | L211                       | Radial inductor                         | LRA561K                    |      |                                   |                            |

|       | F201                       | 1.75MHz L.P.F.                          | VTF1021                    |      | C257, C265, C270, C272, C281,     |                            |

|       | F401                       | Audio B.P.F                             | VTF1025                    |      | C282 C284, C298, C300, C310,      |                            |

|       | F402                       | 2.3MHz B.P.F                            | VTF1026                    |      | C314, C316, C325, C330, C331,     |                            |

|       | F403                       | 2.8MHz B.P.F                            | VTF1003                    |      | C403, C404, C454, C455, C468      |                            |

|       | F3, F4                     | 3 terminal filter                       | VTH1001                    |      | C467                              | CFTXA224J50                |

|       | F1, F2, F5                 | Ferrite bead                            | DTF1003                    |      | C203, C216, C293, C438            | CFTXA104J50                |

|       | ,, . 0                     | J                                       | <del></del>                |      | C292, C35, C334                   | CFTXA473J50                |

|       |                            |                                         |                            |      | C22, C242, C244, C446, C447       | CKPUYB102K5                |

| CAPA  | CITORS                     |                                         |                            |      | C217, C218, C237, C238, C240,     | CKPUYF103Z2                |

|       |                            |                                         |                            |      | C250, C267, C268, C401, C402      | 0111 011 1002              |

| Mark  | Symbol & De                | escription                              | Part No.                   |      | 0200, 0207, 0200, 0101, 0102      |                            |

|       | C23, C36                   |                                         | CCCCH040D50                |      | C4, C10, C15, C28, C32, C37,      | CKPUYF223Z2                |

|       | C20, C14                   |                                         | CCCCH060D50                |      | C202, C205, C207, C223, C225,     |                            |

|       | C213                       |                                         | CCCCH080D50                |      | C227, C230, C235, C248, C251,     |                            |

|       | C241 C335                  |                                         | CCCCH080D50                |      | C254, C258, C259 C264, C266,      |                            |

|       | C44, C303,                 | C318                                    | CCCCH101J50                |      | C269, C280, C283, C291, C294,     |                            |

|       | 011, 0000,                 |                                         |                            |      | C297, C302, C304, C309, C313,     |                            |

|       | C215, C338                 | C317                                    | CCCCH120J50                |      | C315, C319, C321, C340, C341,     |                            |

|       | C213, C338                 | , 0017                                  | CCCCH121J50                |      | C405, C406, C410 — C413, C434,    |                            |

|       |                            | C289                                    |                            |      |                                   |                            |

|       | C234, C239                 |                                         | CCCCH150J50                |      | C435, C456, C457, C469, C470      |                            |

|       |                            | , C247, C274                            | CCCCH180J50<br>CCCCH220J50 |      | CE C6 C0                          | COMA 102 IEO               |

|       |                            |                                         | . T T C = 220 150          |      | C5, C6, C9                        | CQMA102J50                 |

|       | C232, C233                 |                                         | CCCC11220350               |      |                                   | CON44 100 IEC              |

|       | C273                       |                                         |                            | ,    | C278                              | CQMA103J50                 |

|       | C273<br>C339, C337         |                                         | CCCCH270J50                | ,    | C278<br>C420, C421                | CQMA152J50                 |

|       | C273<br>C339, C337<br>C214 |                                         | CCCCH270J50<br>CCCCH330J50 | ,    | C278<br>C420, C421<br>C18         | CQMA152J50<br>CQMA182J50   |

|       | C273<br>C339, C337         | , C26                                   | CCCCH270J50                | ,    | C278<br>C420, C421                | CQMA152J50                 |

| Mark    | Symbol & D         | escription            | Part No.                 | COILS | 3                |                            |                                                    |

|---------|--------------------|-----------------------|--------------------------|-------|------------------|----------------------------|----------------------------------------------------|

|         | C448               |                       | CQMA222J50               | Mark  | Symbol &         | Description                | Part No.                                           |

|         | C277               |                       | CQMA272J50               |       | VL101            | Variable coil (3.8μH)      | VTL-275                                            |

|         | C21, C27           |                       | CQMA392J50               |       | VE101            | Variable con (orogin)      |                                                    |

|         | C432, C43          |                       | CQMA393J50               |       | L101             | Coil (4.7µH)               | VTL1003                                            |

|         | C426 — C4          | 29                    | CQMA472J50               |       |                  |                            |                                                    |

|         | C287, C46;<br>C220 | 3                     | CQMA683J50<br>CQSA821J50 | CAPA  | CITORS           |                            |                                                    |

|         | 0220               |                       |                          | Mark  | Symbol &         | Description                | Part No.                                           |

|         | VC1, VC2           | Ceramic trimmer (20P) | VCM-008                  |       | C201. C2         | 03, C204                   | CCCCH220J50                                        |

|         |                    |                       |                          |       | C118             |                            | CCCCH560J50                                        |

| RESIS   | TORS               |                       |                          |       | C107             |                            | CCCSL331J50                                        |

| RESIS   | _                  |                       |                          |       | C119             |                            | CCCSL391J50                                        |

| Mark    | Symbol & D         | escription            | Part No.                 |       | C104             |                            | CCCUJ221J50                                        |

|         | VR202              | Semi-fixed (1kΩ)      | VRTB6VS102               |       | C103 C1          | 20 (202                    | CCCUJ330J50                                        |

|         | VR201, VR          | 204, VR401 Semi-fixed | VRTG6HS102               |       | C103, C1<br>C113 | 20, 6202                   | CEANP2R2M50                                        |

|         |                    | (1kΩ)                 |                          |       |                  | 26                         | CEANP220M16                                        |

|         | VR203              | Semi-fixed (4.7kΩ)    | VRTG6HS472               |       | C216, C2<br>C110 | 20                         | CEAS010M50                                         |

|         |                    |                       |                          |       |                  | 09, C116, C117, C122       | CEAS100M50                                         |

|         | R219 R2            | 21, R223, R225, R234, | RN1/6PQ□□□□F             |       | C100. C1         | 00, 0110, 0117, 0122       | <b>31</b> , 13 1 1 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|         | R248, R249         | 9, R251, R252, R483,  |                          |       | C121, C1         | 25, C127, C205             | CEAS101M10                                         |

|         | R485               |                       |                          |       | C211, C2         |                            | CEAS220M25                                         |

|         |                    | Other resistors       | RD1/6PM□□□J              |       |                  | 06, C209, C210,            | CEAS47OM16                                         |

|         |                    |                       |                          |       |                  | 220, C227 — C230           |                                                    |

| OTHE    | RS                 |                       |                          |       | C112             |                            | CFTXA1O4J50                                        |

| Mark    | Symbol & D         | escription            | Part No.                 |       | C115             |                            | CFTXA474J50                                        |

| IVICI K | <u> </u>           |                       |                          |       | C212, C2         | 22                         | CFTXA683J50                                        |

|         | JA3                | Pin jack (2Pin)       | DKB1010                  |       | C101, C1         |                            | CGCYX473M25                                        |

|         | JA1, JA2           | Pin jack (2Pin)       | DKB1011                  |       | C214, C2         | 24                         | CKCYB561K50                                        |

|         | X1                 | Crystal resonator     | VSS1005                  |       | C215, C2         | 25                         | CKCYB681K50                                        |

|         | DL201              | 220nsec Delay line    | VTF-063                  |       |                  |                            |                                                    |

|         |                    | BNC assembly          | DKN1018                  |       | C102, C2         |                            | CKCYF1O3Z50                                        |

|         |                    | BNC holder            | DNF1152                  |       | C111, C2         | 13, C223                   | COMA103J50                                         |

|         |                    | DIVO HOIGEI           | 5111 1102                |       | C231             |                            | CQMA 10 4 J 50                                     |

|         |                    |                       |                          |       | C106             |                            | CQMA 22 3 J 50                                     |

|         |                    |                       |                          |       | C114             |                            | CQMA82 2J50                                        |

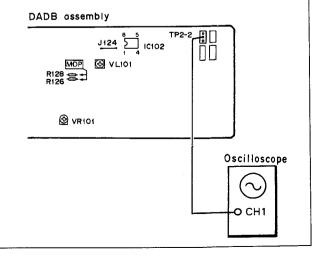

|         |                    | y (DWV1034)           | David No.                | preid | TORC             |                            |                                                    |

| Mark_   | Symbol & D         | Description           | Part No.                 |       | STORS            |                            | Down No.                                           |

|         | IC110              |                       | BU4053B                  | Mark  | Symbol &         | Description                | Part No.                                           |

|         | IC104              |                       | CXD1130Q                 |       | VR101            | Semi-fixed (22k $\Omega$ ) | VRTB6VS223                                         |

|         | IC105              |                       | CXK5816M-12L<br>LC7881-C |       |                  |                            |                                                    |

|         | IC107              | 00                    | M5218P                   |       | R114, R1         | 15, R118, R120, R127,      | RN1/6PQ □□□□F                                      |

|         | IC108, IC1         | O9                    | W152 T 6F                |       | R128, R1         | 38                         |                                                    |

|         | IC102, IC1         | 03                    | NJM082D                  |       |                  | Other resistors            | RD1/6PVI□□□J                                       |

|         | IC111              |                       | NJM78L05A                |       |                  | •                          |                                                    |

|         | IC112              |                       | NJM79L05A                |       |                  |                            |                                                    |

|         | IC106              |                       | PDE024                   | OTHE  | R                |                            |                                                    |

|         | IC101              |                       | TC40H004P                | Mark  |                  | Description                | Part No.                                           |

|         | 0000               |                       | 2SA933S                  | Wark  | <u> </u>         | Безоприон                  |                                                    |

|         | Q203<br>Q201, Q20  | 2                     | 2SC1740S                 |       | X1 Crys          | tal resonator (16MHz)      | VSS10(4                                            |

|         | D102               |                       | FC54M                    |       |                  |                            |                                                    |

|         | D102<br>D101       |                       | KV1225YBR                |       |                  |                            |                                                    |

|         |                    | 4, D201, D202         | 1\$\$254                 |       |                  |                            |                                                    |

|         | D 100, D 10        | -, 5201, 5202         | .0020.                   |       |                  |                            |                                                    |

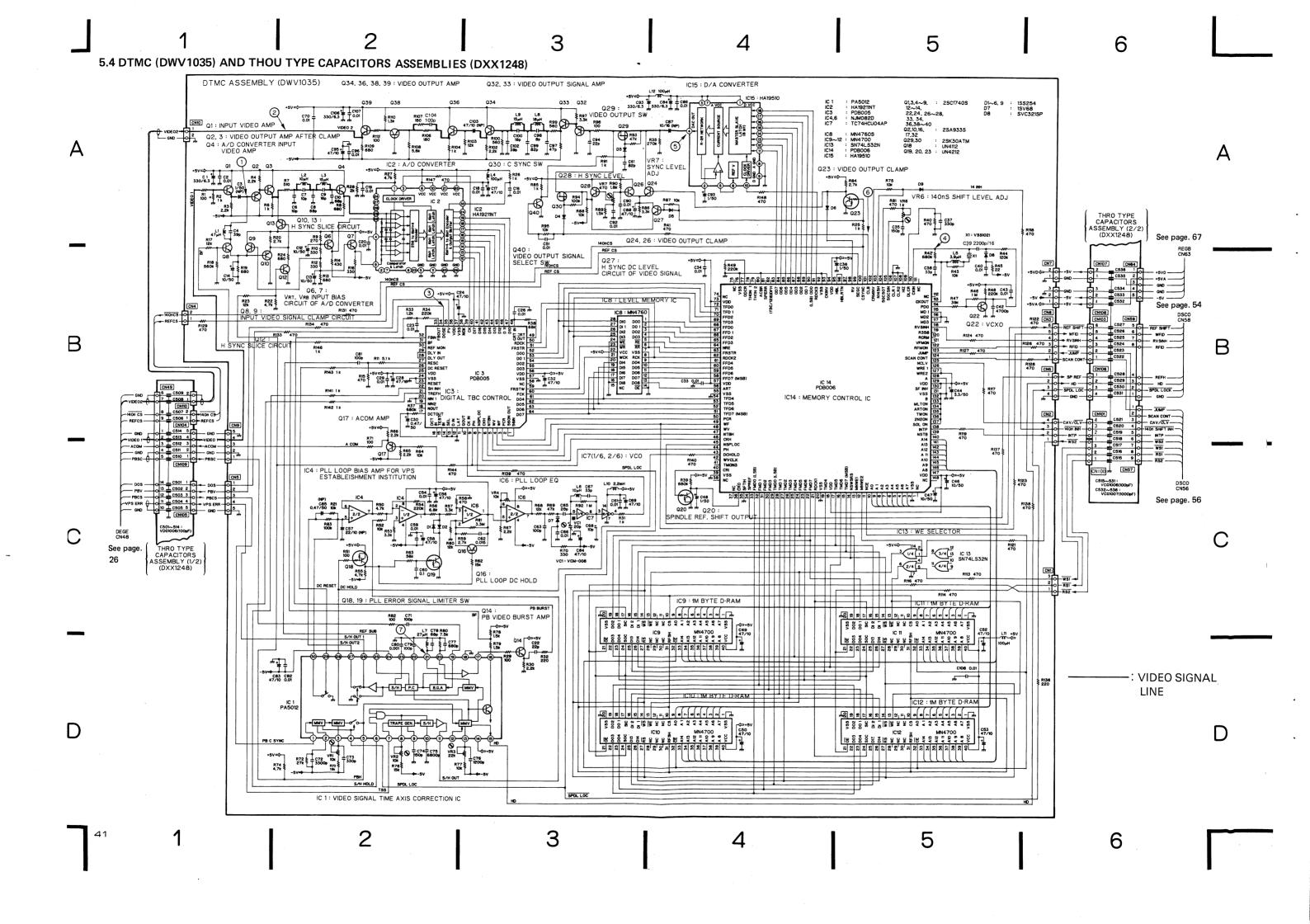

# DTMC Assembly (DWV1035) SEMICONDUCTORS

| Mark          | Symbol &                                           | Description             | Part No.                                                                                      | Mark         | Symbol & De       | scription                  | Part No.                                      |

|---------------|----------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------|--------------|-------------------|----------------------------|-----------------------------------------------|

|               | IC2                                                |                         | HA19211NT                                                                                     |              | СЗ                |                            | CEANPO10M50                                   |

|               | IC15                                               |                         | HA19510                                                                                       |              | C87               |                            | CEANP100M16                                   |

|               | IC9 — IC1                                          | 12                      | MN4700                                                                                        |              | C57               |                            | CEANP220M10                                   |

|               | IC8                                                | . –                     | MN4760S                                                                                       |              | C103              |                            | CEANP470M10                                   |

|               | IC4, IC6                                           |                         | NJM082D                                                                                       |              | C36, C93, C       | 48                         | CEAS010M50                                    |

|               | IC1                                                |                         | PA5012                                                                                        |              | C12 — C14,        | C46. C47                   | CEAS100M50                                    |

|               | IC3                                                |                         | PDB005                                                                                        |              | C30               | 0.0,01,                    | CEASR47M50                                    |

|               | IC14                                               |                         | PDB006                                                                                        |              | C44               |                            | CEAS3R3M50                                    |

|               | IC13                                               |                         | SN74LS32N                                                                                     |              | C1, C91, C1       | ne C84                     | CEAS331M6R3                                   |